CAEN VX1190A TDC

CAEN VX1190A multihit TDC, 96 channels

User Manual

File:VX1190A UserManualRev13.pdf

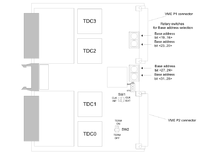

Addressing

From the picture and the above diagram it looks like the module is at the following settings

<bits 19-16>=0x01

<bits 23-20>=0x02

<bits 27-24>=0x08

<bits 31-29>=0x00

ROL initializing

# Address for TDC CAEN 1190

const NC1190 = 1

const C1190_ADDR = 0x210000

const C1190_OFFSET = 0x10000

# Maximum number of 32bit words from C1190

const C1190_MAX_DATA = 128

const C1190_BLOCK_READ = 1

# Note that C1190_ADDR must be A32 for 2eSST, A24 okay for BLT/MBLT

tdc1190Init(C1190_ADDR,C1190_OFFSET,NC1190,1);

tdc1190SetTriggerMatchingMode(i);

tdc1190SetEdgeResolution(i,100);

tdc1190EventFifo(i,0); /* Must be enabled(disabled) for Linked List (direct) DMA */

tdc1190SetBLTEventNumber(i,C1190_BLOCK_READ);

output from ROC_CODA when after download

Initialized TDC ID 0 at address 0xa6b79000 tdc1190SetEdgeResolution(0): Set Edge Resolution to 100 ps

Errors

invalid event pointer

tdc1190ReadBlock: ERROR in DMA transfer Initialization 0xffffffff jlabgefDmaSend: ERROR: the_event pointer is invalid!

gen_int_list.crl

#

# General User readout list

#

# David Abbott, TJNAF 2000

readout list GEN_USER

maximum 1024,512

general readout

# A16 Address for SIS3610 Module

const TRIG_ADDR=0x3800

# Address for TDC CAEN 1190

const NC1190 = 1

const C1190_ADDR = 0x210000

const C1190_OFFSET = 0x10000

# Maximum number of 32bit words from C1190

const C1190_MAX_DATA = 128

const C1190_BLOCK_READ = 1

# Note that C1190_ADDR must be A32 for 2eSST, A24 okay for BLT/MBLT

extern int bigendian_out;

begin download

variable res, i

vmeOpenDefaultWindows();

s3610Init(TRIG_ADDR,0,0);

# When sending to a Linux Host set bigendian_out = 0

bigendian_out = 1;

log inform "Initializing TDC 1190"

# SETUP caen1190

%%

tdc1190Init(C1190_ADDR,C1190_OFFSET,NC1190,1);

tdc1190SetTriggerMatchingMode(0);

tdc1190SetEdgeResolution(0,100);

tdc1190EventFifo(0,0); /* Must be enabled(disabled) for Linked List (direct) DMA */

tdc1190SetBLTEventNumber(0,C1190_BLOCK_READ);

tdc1190BusError(0,C1190_BLOCK_READ); /* 1: BERR/2eTERM for block reads (DMA), 0 for SCT */

/* tdc1190SetWindowWidth(0,51176); */

/* tdc1190SetWindowOffset(0,-800001); */

%%

log inform "User Download Executed"

end download

begin prestart

variable jj, adc_id

log inform "Entering User Prestart"

init trig source GEN

link async trig source GEN 1 to usrtrig and usrtrig_done

event type 1 then read GEN 1

%%

tdc1190Status(0);

%%

log inform "User Prestart Executed"

end prestart

begin end

CDODISABLE(GEN,1,1);

log inform "User End Executed"

end end

begin pause

CDODISABLE(GEN,1,1);

log inform "User Pause Executed"

end pause

begin go

log inform "Entering User Go"

CDOENABLE(GEN,1,1);

end go

begin trigger usrtrig

variable ii, event_ty, event_no, datascan, imod, nwrds

variable evStored

rol->dabufp = (long *) 0;

open event type EVTYPE of BT_UI4

%%

/* Check for valid data here */

for(ii=0;ii<100;ii++)

{

datascan = tdc1190Dready(0);

if (datascan>0)

{

break;

}

}

if(datascan>0)

{

// Get the TDC data from all modules... rflag=1 block read, 0 for SCT

for(imod=0;imod<1;imod++)

{

nwrds = tdc1190ReadBlock(imod,rol->dabufp,C1190_MAX_DATA,C1190_BLOCK_READ);

if(nwrds < 0)

{

logMsg("ERROR: in transfer (event = %d), status = 0x%x\n",

event_no,nwrds);

*rol->dabufp++ = 0xda000bad;

}

else

{

rol->dabufp += nwrds;

}

}

}

else

{

evStored = tdc1190GetEventStored(0);

logMsg("ERROR: Data not ready in event %d evStored = %d\n",event_no,evStored);

*rol->dabufp++ = 0xda000bad;

}

%%

close event

end trigger

begin done usrtrig

end done

begin done

# Re-enable Trigger Source here

s3610IntAck(1);

end done

begin status

end status

ROC EB crash when component released

When the r1dc components are released from the CODA GUI in order to reload the r1dc readoutlist , the SIS3610 will have its VU light go green, CODA_ROC and CODA_EB will crash.

The error message printed to the screen by CODA_EB is

thread exit for rocdaq1 get_cb_data returned end of file ROC mask 8 force_end 2 Segmentation fault

Data Record

General Header:

- bits 0->4 = GEO =0x01000

- bits 5->26 = Event counter

- bits 27->31 = global header = 01000

0x400083a8 = 1000000000000001000001110101000

event number = 0x0000000000010000011101 = 0x41d

0x400083c8 = 1000000000000001000001111001000

event number = 0000000000010000011110 = 0x41E

0x400083e8=1000000000000001000001111101000

event number = 0000000000010000011111 = 0x41F

TDC header

- bits 0->11 = Bunch ID

- bits 12->23 = event id

- bits 24->25 = TDC

- bit 26 nothing

- bits 27->31 = 0x00001

0x841d563 = 0001000010000011101010101100011

TDC = 00 event id=010000011101=41D

0x841efe2 = 0001000010000011110111111100010

00 010000011110=41E

0x841f39f=0001000010000011111001110011111

0001 0 TDC=00 event id=010000011111=41F bunch id=001110011111

TDC measurement

- bits 0->18 = measurement

- bits 10->25= channel

- bit 26: leadng or trailing

- bits 27->31 = 00000

TDC trailer

- bits 0->11 = word count

- bits 12->23 = event ID

- bits 24->25 - TDC

- bits 26 nothing

- bits 27->31 = 0x00011

0x1841d002 =00011000010000011101000000000010

TDC error

bits:0->14 Error flag

- bits 15->23 = blank

- bits 24->25 = TDC #

- bit 26 blank

- bits 27->31=0x00100