CAEN V488 TDC

Jump to navigation

Jump to search

The 12 bit ADC conversion time is 5.7 s. A sliding scale technique is used to reduce differential nonlinearity by injecting an offset. This reduces the dynamic range to 0 3840. ADC values between 3841 and 4095 indicate an error.

The TDC measures the time interval between the falling ECL inputs to the start/stop and the channel.

You can change the dynamic range of the TDC by setting bits using the library function c775setFSR.

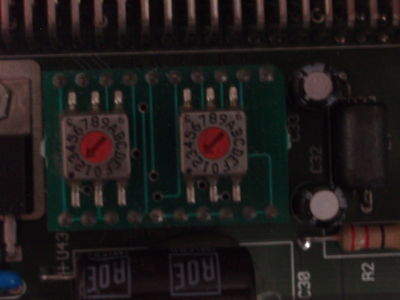

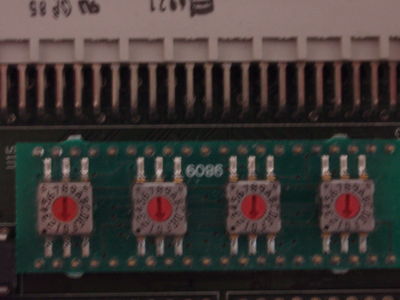

| Address | |

| Pin | Setting |

| SW 1 | 2 |

| SW 2 | 2 |

| SW 3 | 0 |

| SW 4 | 0 |

initialize TDC

-> c775Init(0x610000) Initialized TDC ID 0 at address 0x90610000