CAEN VX1190A TDC

CAEN VX1190A multihit TDC, 96 channels

User Manual

File:VX1190A UserManualRev13.pdf

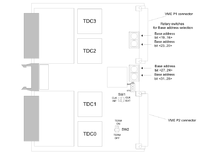

Addressing

From the picture and the above diagram it looks like the module is at the following settings

<bits 19-16>=0x01

<bits 23-20>=0x02

<bits 27-24>=0x08

<bits 31-29>=0x00

ROL initializing

# Address for TDC CAEN 1190

const NC1190 = 1

const C1190_ADDR = 0x210000

const C1190_OFFSET = 0x10000

# Maximum number of 32bit words from C1190

const C1190_MAX_DATA = 128

const C1190_BLOCK_READ = 1

# Note that C1190_ADDR must be A32 for 2eSST, A24 okay for BLT/MBLT

tdc1190Init(C1190_ADDR,C1190_OFFSET,NC1190,1);

tdc1190SetTriggerMatchingMode(i);

tdc1190SetEdgeResolution(i,100);

tdc1190EventFifo(i,0); /* Must be enabled(disabled) for Linked List (direct) DMA */

tdc1190SetBLTEventNumber(i,C1190_BLOCK_READ);

output from ROC_CODA when after download

Initialized TDC ID 0 at address 0xa6b79000 tdc1190SetEdgeResolution(0): Set Edge Resolution to 100 ps