Difference between revisions of "Warren Parsons Log Book"

| (166 intermediate revisions by 2 users not shown) | |||

| Line 2,402: | Line 2,402: | ||

==Run 1534 2 PMTs in coinc== | ==Run 1534 2 PMTs in coinc== | ||

| − | Began run at 14: | + | Began run at 14:35 pm on April 19, 2010 |

GEM HV is at 3000 kV on both drift and GEM. With equal HV settings GEM is essentially turned off. | GEM HV is at 3000 kV on both drift and GEM. With equal HV settings GEM is essentially turned off. | ||

| Line 2,438: | Line 2,438: | ||

| + | ==Run 1535 2 PMTs in coinc== | ||

| + | |||

| + | Began run at 15:06 pm on April 19, 2010 | ||

| + | |||

| + | GEM HV is at 3000 kV on both drift and GEM. With equal HV settings GEM is essentially turned off. | ||

| + | |||

| + | New VFAT settings | ||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd2 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xe5 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd2 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe1 | ||

| + | |} | ||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =2551 | ||

| + | Number of hits in each VFAT card | ||

| + | 0 0 0 0 0 0 | ||

| + | Average number of time VFAT card has data | ||

| + | 0 0 0 0 0 0 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 0 0 0 0 0 0 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 0 0 0 0 0 0 | ||

| + | |||

| + | |||

| + | ==Run 1538 2 PMTs in coinc== | ||

| + | |||

| + | Began run at ???? pm on April 19, 2010 | ||

| + | |||

| + | GEM HV is at 3500/3200 kV on drift and GEM. GEM is turned on. | ||

| + | |||

| + | In trigger: GEMTrig+TwoPMTs. | ||

| + | |||

| + | VFAT settings | ||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd2 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xe5 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd2 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe1 | ||

| + | |} | ||

| + | |||

| + | |||

| + | |||

| + | ==Run 1539 2 PMTs in coinc== | ||

| + | |||

| + | Began run at 16:56 pm on April 19, 2010(end: april 20, 9:53 am) | ||

| + | |||

| + | GEM HV is at 3000 kV on both drift and GEM. With equal HV settings GEM is essentially turned off. | ||

| + | |||

| + | New VFAT settings | ||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd2 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xe5 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd2 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe1 | ||

| + | |} | ||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =101065 | ||

| + | Number of hits in each VFAT card | ||

| + | 0 0 0 0 0 0 | ||

| + | Average number of time VFAT card has data | ||

| + | 0 0 0 0 0 0 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 0 0 0 0 0 0 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 0 0 0 0 0 0 | ||

| + | |||

| + | |||

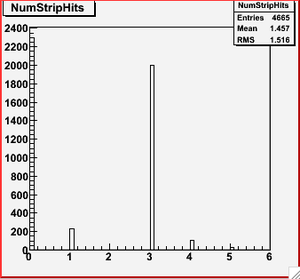

| + | ==Run 1541 PMT+GEM== | ||

| + | |||

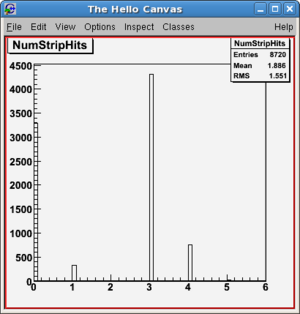

| + | ;VFAT 0 (vfat16) and 3 (vfat80) have the lowest threshold and see most of the hits as shown below | ||

| + | :I suspect the GEM output is too low for the other cards to see because they are too noisy (thresholds too high). Let's increase GEM HV to 3600 and check what happens to the average hits per card. | ||

| + | |||

| + | |||

| + | At 3600 Volts detector sparks, i prefer not to have it so high. | ||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd2 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xe5 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd2 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe1 | ||

| + | |} | ||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =472 | ||

| + | Number of hits in each VFAT card | ||

| + | 299 35 0 272 14 6 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.633475 0.0741525 0 0.576271 0.029661 0.0127119 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 2295 229 0 2004 104 28 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 7.67559 6.54286 0 7.36765 7.42857 4.66667 | ||

| + | |||

| + | |||

| + | [[File:VFAT1.jpg|300px]] | ||

| + | |||

| + | |||

| + | ended run at 9:54 am on 4/22/10 | ||

| + | |||

| + | ==Run 1542 PMT+GEM== | ||

| + | |||

| + | |||

| + | Began run at 10:03 am 4/22/10 | ||

| + | |||

| + | GEM HV at 3575 | ||

| + | |||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd2 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xe5 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd2 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe1 | ||

| + | |} | ||

| + | |||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =877 | ||

| + | Number of hits in each VFAT card | ||

| + | 499 48 0 504 50 6 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.568985 0.054732 0 0.574686 0.0570125 0.00684151 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 3284 326 0 4318 757 28 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 6.58116 6.79167 0 8.56746 15.14 4.66667 | ||

| + | |||

| + | [[File:Vfat2.png|300px]] | ||

| + | |||

| + | ==Run 1544 2PMT+GEM== | ||

| + | |||

| + | |||

| + | Began run at 16:57 pm 4/22/10, end at 13:53 pm 4/23/10 | ||

| + | |||

| + | GEM HV at 3575 | ||

| + | |||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd2 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xe5 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd2 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe1 | ||

| + | |} | ||

| + | |||

| + | |||

| + | Number of events: '''28''' | ||

| + | |||

| + | ==Run 1546 GEM+2PMT== | ||

| + | |||

| + | |||

| + | Began run at 15:18 pm 4/23/10, | ||

| + | GEM HV at 3575 | ||

| + | |||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd2 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xe5 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd2 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe1 | ||

| + | |} | ||

| + | |||

| + | At 9:35 am on 4/24/10 we had about 428 events | ||

| + | |||

| + | <pre> | ||

| + | Number of Events =428 | ||

| + | Number of hits in each VFAT card | ||

| + | 195 9 0 205 32 1 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.455607 0.021028 0 0.478972 0.0747664 0.00233645 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 810 54 0 1765 489 1 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 4.15385 6 0 8.60976 15.2812 1 | ||

| + | </pre> | ||

| + | |||

| + | |||

| + | VFAT card 2 (vfat64) has no hits. I will lower threshold on VFAT card 2 and VFAT card 5. | ||

| + | |||

| + | VFAT card 1 has too few hits , I will lower just 1 bit. | ||

| + | |||

| + | ==Run 1547 GEM+2PMT== | ||

| + | |||

| + | |||

| + | Began run at 9:56 am 4/24/10, | ||

| + | GEM HV at 3575 | ||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd1 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xd0 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd2 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xb8 | ||

| + | |} | ||

| + | <pre> | ||

| + | |||

| + | Number of Events =957 | ||

| + | Number of hits in each VFAT card | ||

| + | 448 17 202 454 45 177 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.46813 0.0177638 0.211076 0.474399 0.0470219 0.184953 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 2000 178 2745 3174 530 3895 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 4.46429 10.4706 13.5891 6.99119 11.7778 22.0056 | ||

| + | </pre> | ||

| + | |||

| + | |||

| + | Lower the threshold on 1 (2% hit rate) and 4 (5% hit rate) | ||

| + | |||

| + | Raise the threshold on 2 (14% strip hit /event) and 5 (22%) | ||

| + | |||

| + | After looking at the hits event by event I get the impression that the threshold on VFAT 2 (vfat64) was not so bad. Consider moving back to 0xd0 based on results of next run. | ||

| + | |||

| + | ==Run 1548 GEM+2PMT== | ||

| + | Began run at 9:37 am 4/26/10, | ||

| + | GEM HV at 3575 | ||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd0 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xd6 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd0 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xc5 | ||

| + | |} | ||

| + | |||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =77 | ||

| + | Number of hits in each VFAT card | ||

| + | 10 1 2 12 2 2 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.12987 0.012987 0.025974 0.155844 0.025974 0.025974 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 45 3 15 92 64 22 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 4.5 3 7.5 7.66667 32 11 | ||

| + | |||

| + | ==Run 1549 GEM+2PMT== | ||

| + | |||

| + | |||

| + | Began run at 13:23 pm 4/26/10, <br> | ||

| + | GEM HV at 3575 | ||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xcf | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xd6 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd0 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xc5 | ||

| + | |} | ||

| + | |||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =707 | ||

| + | Number of hits in each VFAT card | ||

| + | 0 0 4 0 0 0 | ||

| + | Average number of time VFAT card has data | ||

| + | 0 0 0.00565771 0 0 0 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 0 0 4 0 0 0 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 0 0 1 0 0 0 | ||

| + | |||

| + | |||

| + | ?????? | ||

| + | |||

| + | ==Run 1550 GEM+2PMT== | ||

| + | |||

| + | |||

| + | Began run at 16:18 pm 4/27/10, <br> | ||

| + | GEM HV at 3575 | ||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xcf | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xd6 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd0 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xc5 | ||

| + | |} | ||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =648 | ||

| + | Number of hits in each VFAT card | ||

| + | 333 43 95 413 61 120 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.513889 0.066358 0.146605 0.637346 0.0941358 0.185185 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 1736 339 554 4574 761 2402 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 5.21321 7.88372 5.83158 11.0751 12.4754 20.0167 | ||

| + | |||

| + | |||

| + | ==Run 1551 GEM+2PMT== | ||

| + | |||

| + | |||

| + | Began run at 10:45 am 4/28/10, <br> | ||

| + | GEM HV at 3575 | ||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xce | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xd5 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xcf | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xc5 | ||

| + | |} | ||

| + | |||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =190 | ||

| + | Number of hits in each VFAT card | ||

| + | 104 21 27 118 20 33 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.547368 0.110526 0.142105 0.621053 0.105263 0.173684 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 611 264 227 1394 182 676 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 5.875 12.5714 8.40741 11.8136 9.1 20.4848 | ||

| + | |||

| + | |||

| + | ==Run 1552 GEM+2PMT== | ||

| + | |||

| + | |||

| + | Began run at 14:55 am 4/28/10, <br> | ||

| + | GEM HV at 3575 | ||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xcd | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xd4 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xce | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xc5 | ||

| + | |} | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =778 | ||

| + | Number of hits in each VFAT card | ||

| + | 382 72 115 474 71 92 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.491003 0.092545 0.147815 0.609254 0.0912596 0.118252 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 1969 623 1078 4842 1033 1782 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 5.15445 8.65278 9.37391 10.2152 14.5493 19.3696 | ||

| + | |||

| + | ==Run 1553 GEM+2PMT== | ||

| + | |||

| + | |||

| + | Began run at 12:01 am 4/29/10, <br> | ||

| + | GEM HV at 3575 | ||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xcb | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xd2 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xcc | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xc5 | ||

| + | |} | ||

| + | |||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =965 | ||

| + | Number of hits in each VFAT card | ||

| + | 525 142 197 593 145 137 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.544041 0.14715 0.204145 0.614508 0.150259 0.141969 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 2908 2329 2192 6469 1917 3069 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 5.53905 16.4014 11.1269 10.9089 13.2207 22.4015 | ||

| + | |||

| + | |||

| + | ==Run 1563 GEM+2PMT== | ||

| + | |||

| + | |||

| + | GEM Disc threshold = 150mV | ||

| + | |||

| + | Began run at 17:18 pm 4/30/10, <br> | ||

| + | GEM HV at 3575 | ||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xc8 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xc8 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xc8 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xc3 | ||

| + | |} | ||

| + | |||

| + | |||

| + | <pre> | ||

| + | Number of Events =237 | ||

| + | Number of hits in each VFAT card | ||

| + | 204 140 176 215 102 153 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.860759 0.590717 0.742616 0.907173 0.43038 0.64557 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 3301 5543 7495 5426 2784 7412 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 16.1814 39.5929 42.5852 25.2372 27.2941 48.4444 | ||

| + | |||

| + | |||

| + | </pre> | ||

| + | |||

| + | |||

| + | I believe the above runs have too many hits in multiple VFAT cards. The difference is that the GEM trigout threshold is higher (150 mV instead of 120mV). I suggest we go back to the threshold which showed zero hits when the detector is off and try again. | ||

| + | |||

| + | ==Run 1564 2 PMTs in coinc + GEM== | ||

| + | |||

| + | Began run at 1:15 pm on mAY 1, 2010 | ||

| + | |||

| + | GEM HV is at 3275 kV on both drift and GEM. | ||

| + | |||

| + | From run 1539: | ||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x81 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd2 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xe5 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x77 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd2 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe1 | ||

| + | |} | ||

| + | |||

| + | ; I left vfat48 at 0xd2 because it already seems low enough with 50% hits. | ||

| + | |||

| + | As I know, we should have 50 % in Vfat64(2) and vfat80(3). The ones which are vertical. | ||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =126 | ||

| + | Number of hits in each VFAT card | ||

| + | 100 81 21 115 36 47 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.793651 0.642857 0.166667 0.912698 0.285714 0.373016 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 1583 2902 311 2857 982 1496 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 15.83 35.8272 14.8095 24.8435 27.2778 31.8298 | ||

| + | |||

| + | |||

| + | ==Run 1565 2 PMTs in coinc + GEM== | ||

| + | |||

| + | Began run at 21:48 pm on mAY 1, 2010 | ||

| + | |||

| + | GEM HV is at 3275 kV on both drift and GEM. | ||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0x83 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd3 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xe3 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0x78 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd2 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe1 | ||

| + | |} | ||

| + | |||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =332 | ||

| + | Number of hits in each VFAT card | ||

| + | 264 170 79 288 112 111 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.795181 0.512048 0.237952 0.86747 0.337349 0.334337 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 3711 4565 1763 6708 2997 3248 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 14.0568 26.8529 22.3165 23.2917 26.7589 29.2613 | ||

| + | |||

| + | |||

| + | |||

| + | I think we should take vfat80 up to 0xa1 and vfat64 down to 0xa1 | ||

| + | |||

| + | take vfat16 up to 0xa1 and vfat48 up to 0xf1 | ||

| + | |||

| + | Leave vfat96 and vfat112 where they are | ||

| + | |||

| + | |||

| + | ==Run 1566 2 PMTs in coinc + GEM== | ||

| + | |||

| + | Began run at 23:06 pm on May 2, 2010 | ||

| + | |||

| + | GEM HV is at 3275 kV on both drift and GEM. | ||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0xa1 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xe6 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xbe | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0xa1 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd2 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe1 | ||

| + | |} | ||

| + | |||

| + | <pre> | ||

| + | Number of Events =60 | ||

| + | Number of hits in each VFAT card | ||

| + | 33 0 46 34 18 16 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.55 0 0.766667 0.566667 0.3 0.266667 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 326 0 2977 477 377 489 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 9.87879 0 64.7174 14.0294 20.9444 30.5625 | ||

| + | </pre> | ||

| + | |||

| + | vfat48 is too high, split the difference between d3 and e6 so set it to e0 | ||

| + | |||

| + | increase vfat64 to 0xce | ||

| + | |||

| + | increase vfat80 to 0xa4 | ||

| + | |||

| + | ==Run 1567 2 PMTs in coinc + GEM== | ||

| + | |||

| + | Began run at 09:41am on May 3, 2010 | ||

| + | |||

| + | GEM HV is at 3275 kV on both drift and GEM. | ||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0xa1 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xe0 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xce | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0xa4 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd2 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe1 | ||

| + | |} | ||

| + | |||

| + | <pre> | ||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =108 | ||

| + | Number of hits in each VFAT card | ||

| + | 69 28 79 70 46 50 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.638889 0.259259 0.731481 0.648148 0.425926 0.462963 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 1162 580 4171 1580 1672 2227 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 16.8406 20.7143 52.7975 22.5714 36.3478 44.54 | ||

| + | </pre> | ||

| + | raise thresholds on all VFATs except for vfat1 | ||

| + | |||

| + | |||

| + | ==Run 1568 2 PMTs in coinc + GEM== | ||

| + | |||

| + | Began run at 16:11 pm on May 3, 2010 | ||

| + | |||

| + | GEM HV is at 3275 kV on GEM. | ||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0xa1 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xe0 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xd8 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0xaa | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd2 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe1 | ||

| + | |} | ||

| + | |||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =242 | ||

| + | Number of hits in each VFAT card | ||

| + | 171 32 146 140 87 75 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.706612 0.132231 0.603306 0.578512 0.359504 0.309917 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 1974 661 6679 1930 2150 2161 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 11.5439 20.6562 45.7466 13.7857 24.7126 28.8133 | ||

| + | |||

| + | |||

| + | ==Run 1569 2 PMTs in coinc + GEM== | ||

| + | |||

| + | Began run at 09:53 am on May 4, 2010 | ||

| + | |||

| + | GEM HV is at 3275 kV on GEM. | ||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0xc8 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xe0 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xda | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0xab | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd4 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe3 | ||

| + | |} | ||

| + | |||

| + | <pre> | ||

| + | |||

| + | Number of Events =60 | ||

| + | Number of hits in each VFAT card | ||

| + | 27 12 34 36 26 26 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.45 0.2 0.566667 0.6 0.433333 0.433333 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 553 268 1476 713 683 1030 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 20.4815 22.3333 43.4118 19.8056 26.2692 39.6154 | ||

| + | </pre> | ||

| + | |||

| + | |||

| + | Lower threshold on VFAT48 | ||

| + | |||

| + | ==Run 1570 2 PMTs in coinc + GEM== | ||

| + | |||

| + | Began run at 5:58 pm on May 4, 2010 | ||

| + | |||

| + | GEM HV is at 3275 kV on GEM. | ||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0xd0 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd6 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xdb | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0xac | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd5 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe4 | ||

| + | |} | ||

| + | |||

| + | <pre> | ||

| + | |||

| + | Number of Events =178 | ||

| + | Number of hits in each VFAT card | ||

| + | 48 98 116 106 60 71 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.269663 0.550562 0.651685 0.595506 0.337079 0.398876 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 435 2766 4516 1291 1739 2220 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 9.0625 28.2245 38.931 12.1792 28.9833 31.2676 | ||

| + | </pre> | ||

| + | |||

| + | |||

| + | |||

| + | vfat 1,2,3 threshold up | ||

| + | |||

| + | ==Run 1571 2 PMTs in coinc + GEM== | ||

| + | |||

| + | Began run at 09:00 am on May 5, 2010 | ||

| + | |||

| + | GEM HV is at 3275 kV on GEM. | ||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0xd0 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd7 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xd6 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0xa6 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd5 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe4 | ||

| + | |} | ||

| + | |||

| + | |||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =104 | ||

| + | Number of hits in each VFAT card | ||

| + | 78 82 84 90 70 72 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.75 0.788462 0.807692 0.865385 0.673077 0.692308 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 3114 5339 4348 3524 3238 3653 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 39.9231 65.1098 51.7619 39.1556 46.2571 50.7361 | ||

| + | |||

| + | |||

| + | ==Run 1572 2 PMTs in coinc + GEM== | ||

| + | |||

| + | Began run at 14:14 pm on May 5, 2010 | ||

| + | |||

| + | GEM HV is at 3275 kV on GEM. | ||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0xd2 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd9 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xd8 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0xa8 | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd7 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe6 | ||

| + | |} | ||

| + | |||

| + | |||

| + | |||

| + | argc=2 | ||

| + | GUI=1 | ||

| + | Number of Events =105 | ||

| + | Number of hits in each VFAT card | ||

| + | 31 54 69 72 38 57 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.295238 0.514286 0.657143 0.685714 0.361905 0.542857 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 832 2219 3255 1442 841 1945 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 26.8387 41.0926 47.1739 20.0278 22.1316 34.1228 | ||

| + | |||

| + | |||

| + | oops, I made mistake on vfat 2 & 3 by going down instead of up we should set them to 0xdd and 0xaf. | ||

| + | |||

| + | ==Run 1573 2 PMTs in coinc + GEM== | ||

| + | |||

| + | Began run at 8 pm on May 5, 2010 | ||

| + | |||

| + | GEM HV is at 3275 kV on GEM. | ||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0xd2 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xd9 | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xdd | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0xaf | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd7 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe6 | ||

| + | |} | ||

| + | |||

| + | |||

| + | ==Run 1574 2 PMTs in coinc + GEM== | ||

| + | |||

| + | Began run at 09:03 pm on May 5, 2010 | ||

| + | |||

| + | GEM HV is at 3275 kV on GEM. | ||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0xd2 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xdb | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xdd | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0xaf | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd7 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe6 | ||

| + | |} | ||

| + | |||

| + | <pre> | ||

| + | Number of hits in each VFAT card | ||

| + | 56 95 127 97 64 71 | ||

| + | Average number of time VFAT card has data | ||

| + | 0.333333 0.565476 0.755952 0.577381 0.380952 0.422619 | ||

| + | Number of strips hits in each VFAT card | ||

| + | 845 3701 5998 1642 1582 2679 | ||

| + | Average number of strips hit per VFAT card hit | ||

| + | 15.0893 38.9579 47.2283 16.9278 24.7188 37.7324 | ||

| + | |||

| + | </pre> | ||

| + | Thanks for increasing vfat 1. There is no 0xd9 was it 0xd8 or 0xda? | ||

| + | |||

| + | Hopefully this will be the final threshold seting. Tomorrow we will need to see if Warren is ready to do speed tests and S-curves using only 2PMTs in coincidence. | ||

| + | |||

| + | Then pack up the detector to ship it out Friday? | ||

| + | |||

| + | Warren and you can take the electronics in your luggage. | ||

| + | |||

| + | vfat 1 & 2 need to have their thresholds increased | ||

| + | |||

| + | ==Run 1575 2 PMTs in coinc + GEM== | ||

| + | |||

| + | Began run at 09:20 am on May 6, 2010 | ||

| + | |||

| + | GEM HV is at 3275 kV on GEM. | ||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Car # || VFAT ID || VThreshold1 | ||

| + | |- | ||

| + | | 0 ||vfat16 (88ec)|| 0xd2 | ||

| + | |- | ||

| + | | 1 || vfat48 (a6ec)|| 0xdf | ||

| + | |- | ||

| + | | 2 || vfat64 (ca6c)|| 0xe3 | ||

| + | |- | ||

| + | | 3 || vfat80 (96ec)|| 0xaf | ||

| + | |- | ||

| + | | 4 || vfat96 (a66c)|| 0xd7 | ||

| + | |- | ||

| + | | 5 || vfat112 (b8ec)|| 0xe6 | ||

| + | |} | ||

| + | |||

| + | =Raw S-Curve Results= | ||

| + | |||

| + | <table border="1" cellpadding="3"> | ||

| + | <tr><th>vfat16</th><th>vfat48</th><th>vfat64</th><th>vfat80</th><th>vfat96</th><th>vfat112</th></tr> | ||

| + | <tr><td>0x75</td><td>0xb0</td><td>0xb0</td><td>0x70</td><td>0x81</td><td>0x82</td></tr> | ||

| + | <tr><td>0x77</td><td>0xb7</td><td>0xc0</td><td>0x74</td><td>0x82</td><td>0x83</td></tr> | ||

| + | <tr><td>0x78</td><td>0xb8</td><td>0xc5</td><td>0x75</td><td>0x83</td><td>0x87</td></tr> | ||

| + | <tr><td>0x80</td><td>0xc0</td><td>0xc6</td><td>0x76</td><td>0x88</td><td>0xa0</td></tr> | ||

| + | <tr><td>0x81</td><td>0xc1</td><td>0xc8</td><td>0x77</td><td>0xb0</td><td>0xa8</td></tr> | ||

| + | <tr><td>0x81</td><td>0xc2</td><td>0xd0</td><td>0x77</td><td>0xb1</td><td>0xb8</td></tr> | ||

| + | <tr><td>0x81</td><td>0xc2</td><td>0xd5</td><td>0x77</td><td>0xb9</td><td>0xc8</td></tr> | ||

| + | <tr><td>0x81</td><td>0xc2</td><td>0xe5</td><td>0x77</td><td>0xc1</td><td>0xd8</td></tr> | ||

| + | <tr><td>0x81</td><td>0xc2</td><td>0xe5</td><td>0x77</td><td>0xc9</td><td>0xe1</td></tr> | ||

| + | </table> | ||

| + | |||

| + | |||

| + | <table border="1" cellpadding="3"> | ||

| + | <tr><th>vfat16</th><th>vfat48</th><th>vfat64</th><th>vfat80</th><th>vfat96</th><th>vfat112</th></tr> | ||

| + | <tr><td>0.0446855</td><td>0.04726</td><td>0.607025</td><td>0.0441339</td><td>0.49007</td><td>0.786686</td></tr> | ||

| + | <tr><td>0.0433996</td><td>0.0427969</td><td>0.156118</td><td>0.0464135</td><td>0.678722</td><td>0.714888</td></tr> | ||

| + | <tr><td>0.0270423</td><td>0.0326015</td><td>0.0801847</td><td>0.0202582</td><td>0.522472</td><td>0.519646</td></tr> | ||

| + | <tr><td>0.0148338</td><td>0.0122762</td><td>0.0654731</td><td>0.0143223</td><td>0.472123</td><td>0.218414</td></tr> | ||

| + | <tr><td>0</td><td>0.000969932</td><td>0.0436469</td><td>0</td><td>0.0160039</td><td>0.107177</td></tr> | ||

| + | <tr><td>0</td><td>0.00353669</td><td>0.0150309</td><td>0</td><td>0.0229885</td><td>0.0291777</td></tr> | ||

| + | <tr><td>0</td><td>0.00486787</td><td>0.00834492</td><td>0</td><td>0.00486787</td><td>0.00834492</td></tr> | ||

| + | <tr><td>0</td><td>0.00486855</td><td>0</td><td>0</td><td>0.00346208</td><td>0.00173104</td></tr> | ||

| + | <tr><td>0</td><td>0.00615006</td><td>0</td><td>0</td><td>0.000615006</td><td>0</td></tr> | ||

| + | <tr><td>0</td><td>0.000806777</td><td>0</td><td>0</td><td>0.000403388</td><td>0</td></tr> | ||

| + | <tr><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td></tr> | ||

| + | <tr><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td></tr> | ||

| + | </table> | ||

| + | |||

| + | =Timing Run Logs= | ||

| + | |||

| + | |||

| + | (50 ns between trig for v1495 and SIS3600) | ||

| + | |||

| + | ==r1589.dat== | ||

| + | |||

| + | 1kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 103395 Events | ||

| + | |||

| + | |||

| + | ==r1590.dat== | ||

| + | |||

| + | 1.5kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 115495 Events | ||

| + | |||

| + | |||

| + | ==r1591.dat== | ||

| + | |||

| + | 2kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 164997 Events | ||

| + | |||

| + | |||

| + | ==r1592.dat== | ||

| + | |||

| + | 2.2kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 179089 Events | ||

| + | |||

| + | |||

| + | ==r1593.dat== | ||

| + | |||

| + | 2.4kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 205919 Events | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | ==r1594.dat== | ||

| + | |||

| + | 2.6kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 204372 Events | ||

| + | |||

| + | |||

| + | |||

| + | ==r1595.dat== | ||

| + | |||

| + | 2.8kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 199265 Events | ||

| + | |||

| + | |||

| + | ==r1596.dat== | ||

| + | |||

| + | 3kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 207272 Events | ||

| + | |||

| + | |||

| + | ==r1597.dat== | ||

| + | |||

| + | 3.5kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 207278 Events | ||

| + | |||

| + | |||

| + | ==r1598.dat== | ||

| + | |||

| + | 4kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 204448 Events | ||

| + | |||

| + | |||

| + | |||

| + | ==r1599.dat== | ||

| + | |||

| + | 4.5kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 244205 Events | ||

| + | |||

| + | |||

| + | ==r1600.dat== | ||

| + | |||

| + | 5kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 210149 Events | ||

| + | |||

| + | |||

| + | ==r1601.dat== | ||

| + | |||

| + | 5.5kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 224369 Events | ||

| + | |||

| + | |||

| + | ==r1602.dat== | ||

| + | |||

| + | 6kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 221562 Events | ||

| + | |||

| + | |||

| + | ==r1603.dat== | ||

| + | |||

| + | 6.5kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 252875 Events | ||

| + | |||

| + | |||

| + | ==r1604.dat== | ||

| + | |||

| + | 7 kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 236152 Events | ||

| + | |||

| + | |||

| + | |||

| + | ==r1605.dat== | ||

| + | |||

| + | 7.5 kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 237635 Events | ||

| + | |||

| + | |||

| + | ==r1606.dat== | ||

| + | |||

| + | 8kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 221957 Events | ||

| + | |||

| + | |||

| + | ==r1607.dat== | ||

| + | |||

| + | 9kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 221492 Events | ||

| + | |||

| + | |||

| + | |||

| + | ==r1608.dat== | ||

| + | |||

| + | 10kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 227185 Events | ||

| + | |||

| + | |||

| + | ==r1609.dat== | ||

| + | |||

| + | 15kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 230474 Events | ||

| + | |||

| + | |||

| + | ==r1610.dat== | ||

| + | |||

| + | 20kHz rep rate | ||

| + | |||

| + | No runtime errors | ||

| + | |||

| + | 272607 Events | ||

| + | |||

| + | Rate was exceeded on DG535 | ||

| + | |||

| + | |||

| + | =DeadTime Measurements= | ||

| + | |||

| + | A measurement was made to determine readout deadtime as a function of the the trigger rate for the V1495 DAQ. To do this a readoutlist was created which only readout the V1495 module. The SIS3610 outputs a logic level on control output #5 when the ROC is busy reading out data. So by comparing the number of Busy/Accept pulses output on SIS3610 control output #5 to the number of trigger pulses sent to the SIS3610 one can determine how many triggers are missed by the DAQ when attempting to readout the V1495 at high trigger rates. | ||

| + | |||

| + | |||

| + | The v260 scaler was not readout through coda but it was read on the ROC during DAQ | ||

| + | |||

| + | -> v260Init(0xda0000) | ||

| + | Initialized SCALER ID 0 at address 0x90da0000 | ||

| + | -> v260Clear(0) | ||

| + | value = 0 = 0x0 | ||

| + | -> v260Status(0,1) | ||

| + | |||

| + | Proceedure to measure deadtime: | ||

| + | |||

| + | Pause DAQ | ||

| + | |||

| + | clear Scaler | ||

| + | set desired trigger rate | ||

| + | resume CODA | ||

| + | after enough statistics | ||

| + | v260Status(0,1) | ||

| + | then pause code | ||

| + | then repeat | ||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Trigger Rate||Number of Triggers|| Number of Accept pulses || Deadtime | ||

| + | |- | ||

| + | | 4 kHz || 667334 || 667334 | ||

| + | |- | ||

| + | | 5 kHz || 663502 || 663501 | ||

| + | |- | ||

| + | | 7 kHz || 1973929 || 1932025 | ||

| + | |- | ||

| + | | 8 kHz ||402181 || 380583 | ||

| + | |- | ||

| + | | 10 kHz || 342550|| 171274 | ||

| + | |- | ||

| + | | 12 kHz || 1457791 || 721358 | ||

| + | |- | ||

| + | | 14 kHz || 483899 || 236885 | ||

| + | |} | ||

| + | |||

| + | |||

| + | Second Run of Numbers | ||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Trigger Rate||Number of Triggers|| Number of Accept pulses || Deadtime | ||

| + | |- | ||

| + | | 4 kHz || 687621 || 687620 | ||

| + | |- | ||

| + | | 5 kHz || 667417 || 667416 | ||

| + | |- | ||

| + | | 7 kHz || 1144826 || 1122218 | ||

| + | |- | ||

| + | | 8 kHz || 858215 || 808121 | ||

| + | |- | ||

| + | | 10 kHz || 349455 || 174726 | ||

| + | |- | ||

| + | | 12 kHz || 1540774 || 770386 | ||

| + | |- | ||

| + | | 14 kHz || 528705 || 258447 | ||

| + | |} | ||

| + | |||

| + | = Remaining Issues = | ||

| + | |||

| + | The following is the "wish list" of items to be completed before the Qweak experiment is up and running. Some of these are essential while others could be left out and the detector would still be functional but issues in the future could arise. | ||

| + | |||

| + | ;I2C not working | ||

| + | ;; - Look over current configuration to make absolutely positive that everything is connected properly | ||

| + | ;; - Finish redesigned I2C board such that we no longer have to worry whether it's correct or not | ||

| + | ;; - Possibly get schematics from Paul to see what protection is in place and possibly how to fix current VFATs | ||

| + | |||

| + | ;Robust, clean, protected power supplies to VFAT boards | ||

| + | ;; Possible fixes: | ||

| + | ;; - Build active/passive, sensing power supply filters | ||

| + | ;; - Build power protection into the VFAT board or NIM module | ||

| + | |||

| + | ;Clean signals on LVDS lines | ||

| + | ;; Possible fixes: | ||

| + | ;; - Research different cable types/configurations | ||

| + | ;; - Research Potential active circuit compensation | ||

| + | |||

| + | ;Delayed signal to query CODA to take data could be done using MVME6100 instead of external hardware | ||

| + | |||

| + | ;No data integrity checks | ||

| + | ;; - Research CRC checksum algorithms | ||

| + | |||

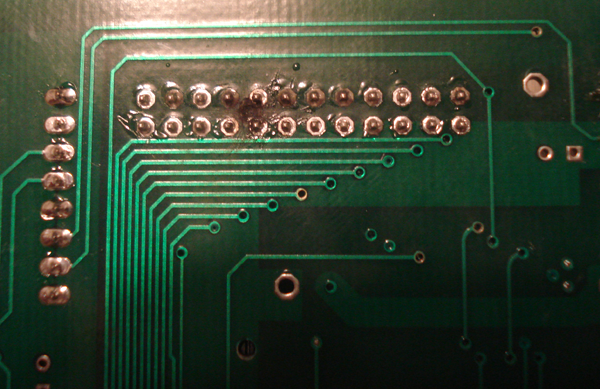

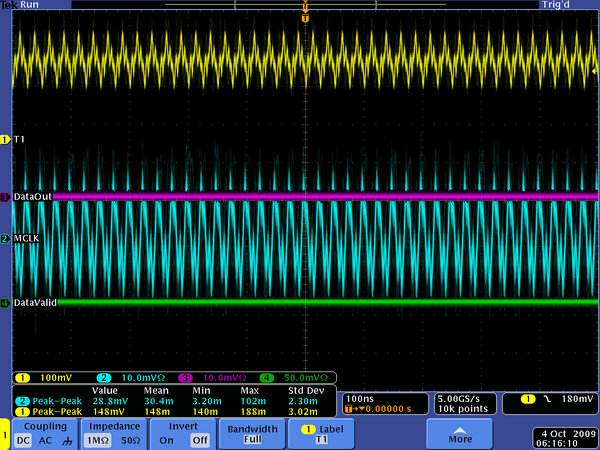

| + | = Cable Impedance Testing 6/30/10 = | ||

| + | |||

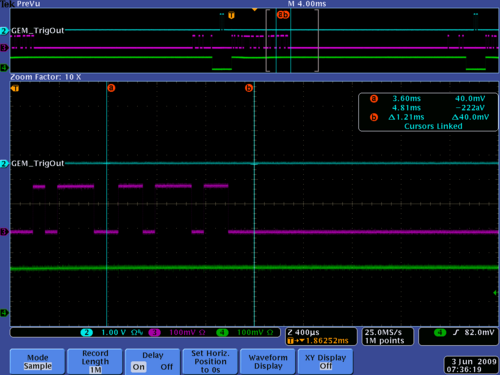

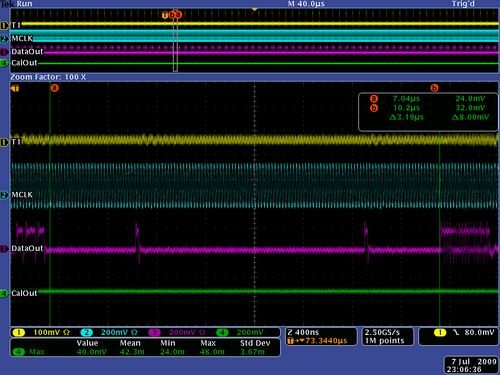

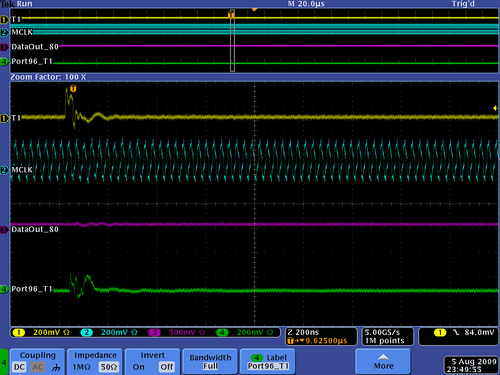

| + | The following pictures were taken using a 50 terminated cable on LDVS signals through our different cables. I am working on how to actually get the impedances correct, so we can actually "see" once and hopefully for all what a properly terminated LVDS input would see on these. I believe that only then can we actually determine how to fix this problem and get the uncorrupted signals back and forth to the VFAT Breakout Boards. | ||

| + | |||

| + | |||

| + | Are the signal cables the same length? | ||

| + | |||

| + | No, they were very different. The unshielded one is the short one that we've been using for a while. | ||

| + | |||

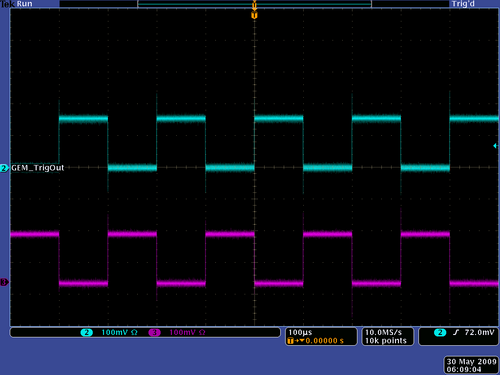

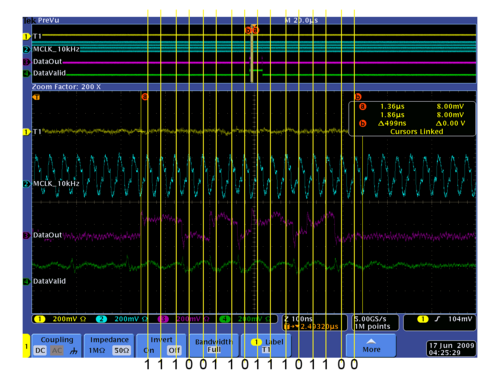

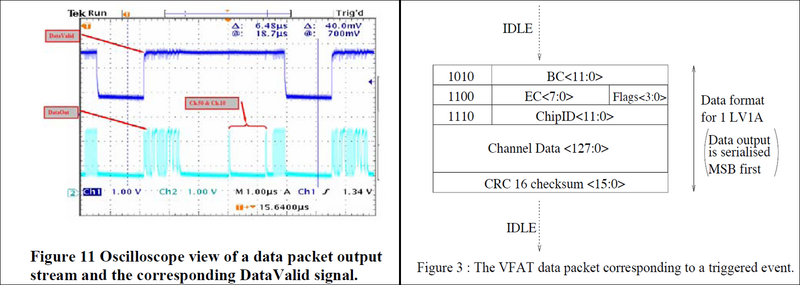

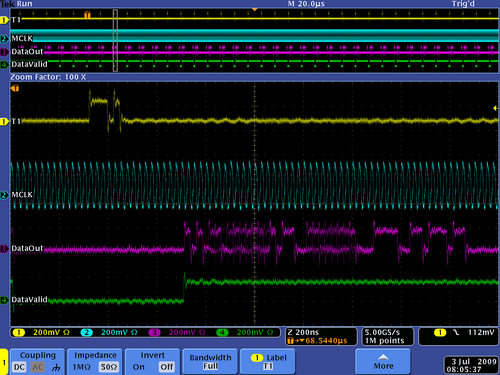

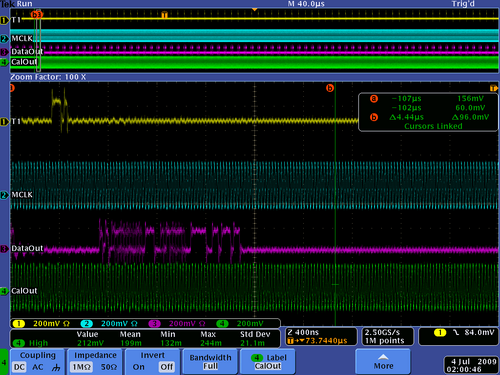

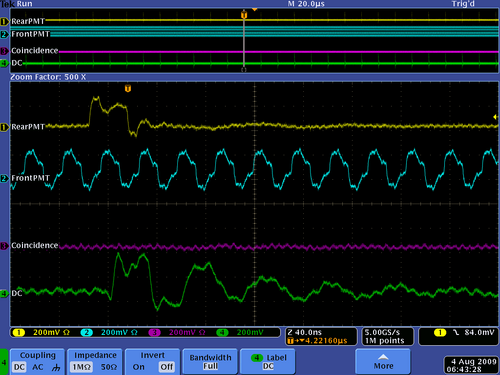

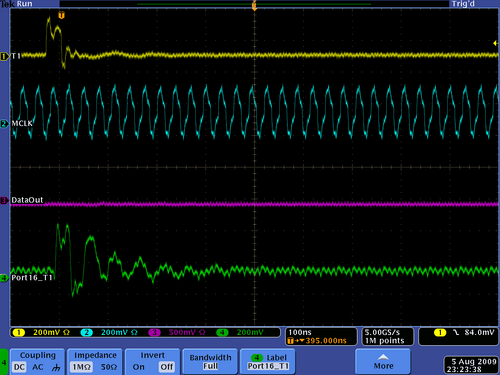

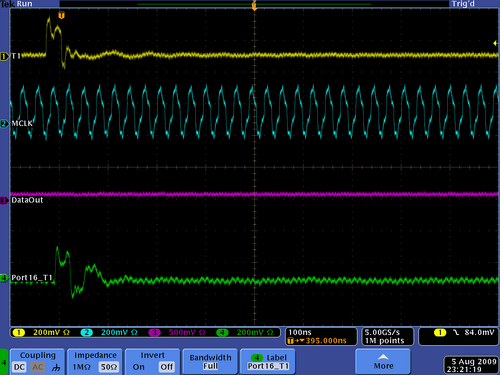

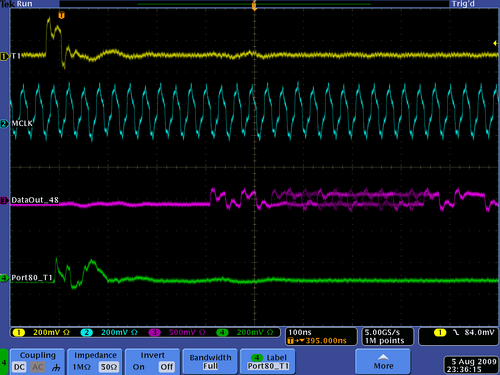

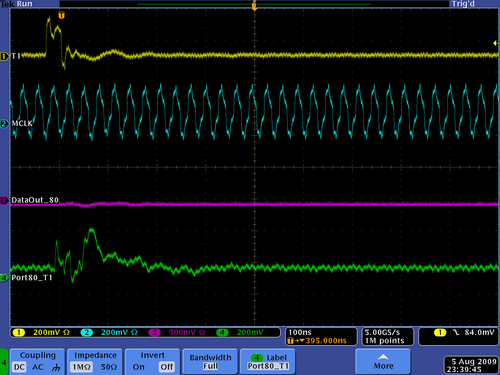

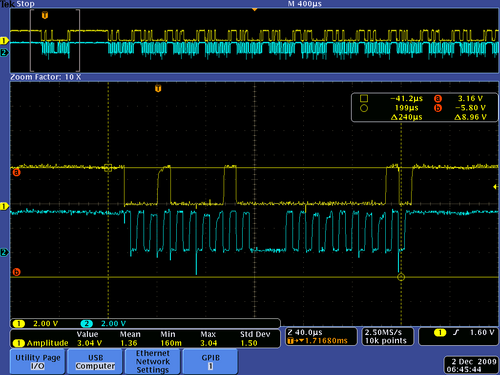

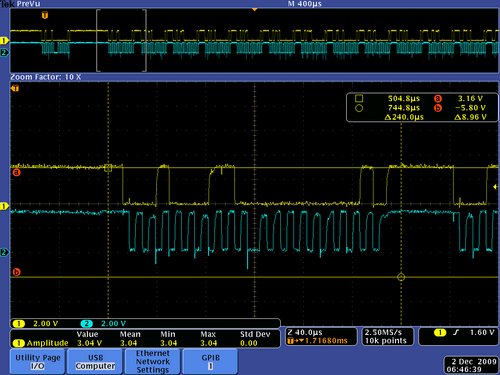

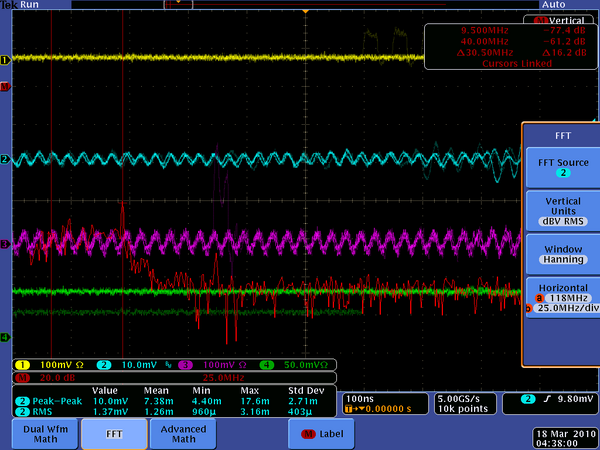

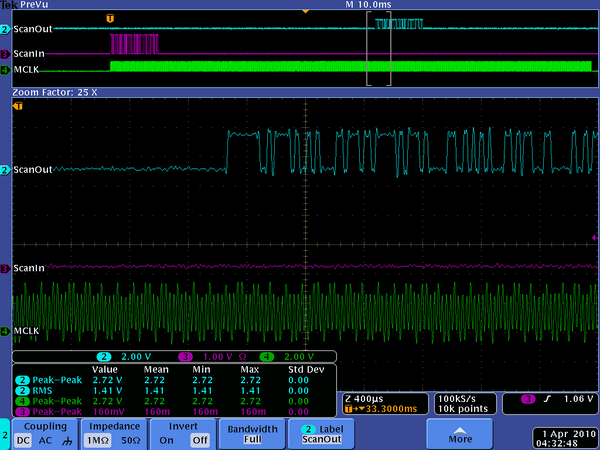

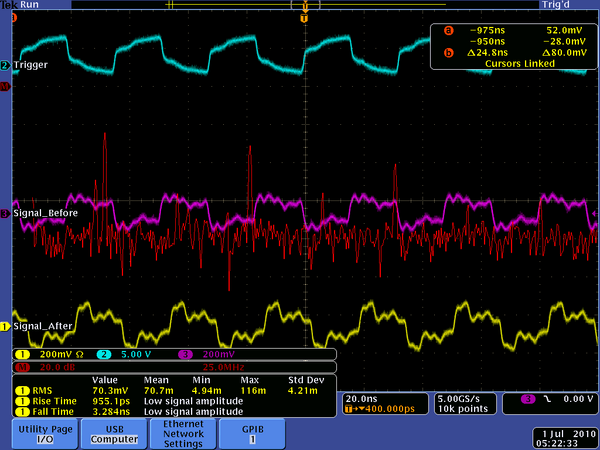

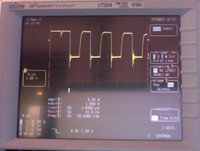

| + | The picture below is for the Unshielded Cable. | ||

| + | |||

| + | [[File:UnshieldedCableTest.png|600px]] | ||

| + | |||

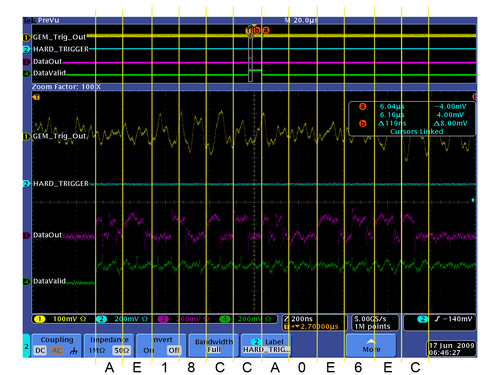

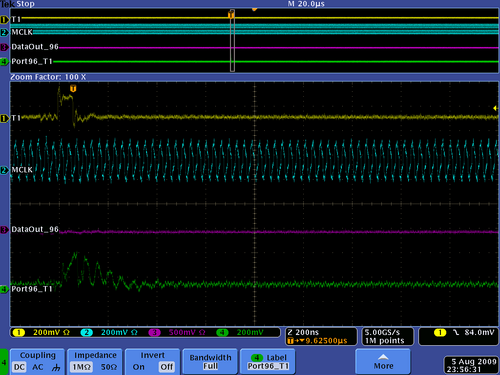

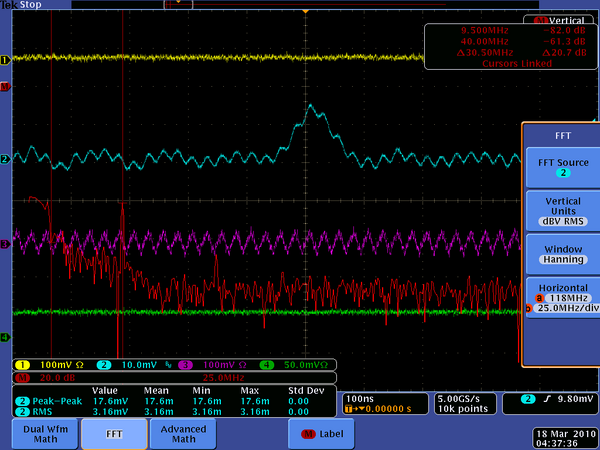

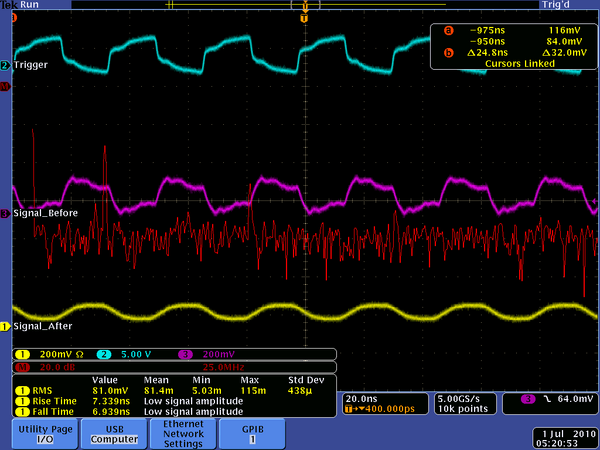

| + | The picture below is for the Shielded Cable. | ||

| + | |||

| + | [[File:ShieldedCableTest.png|600px]] | ||

| + | |||

| + | |||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Cable Crosstalk Data 31 MHz (32.3 ns) | ||

| + | |- | ||

| + | |Unshielded Ribbon Cable (Testing Channel 8) | ||

| + | |- | ||

| + | | Channels Tested || Amplitude (mV RMS) || FFT | ||

| + | |- | ||

| + | | All Channels off || 7.3 || 31 MHz || 62 MHz || 93 MHz || 124 MHz | ||

| + | |- | ||

| + | | Channel 7 only on || 10.4 || -39.1 || -64 || -57.9 || -58 | ||

| + | |- | ||

| + | | All odd on || 15.2 || -45 || -47 || -48 || -60 | ||

| + | |- | ||

| + | | All but 8 on || 21.8 || -46 || -46 || -41.7 || -66 | ||

| + | |- | ||

| + | | Just 8 on || 113 || -22.5 || -59 || -32 || -56 | ||

| + | |- | ||

| + | |||

| + | |||

| + | | Shielded Cable (Also testing Channel 8) | ||

| + | |- | ||

| + | | Channels Tested || Amplitude (mV RMS) || FFT | ||

| + | |- | ||

| + | | All Channels off || 7 || 31 MHz || 62 MHz || 93 MHz || 124 MHz | ||

| + | |- | ||

| + | | Channel 7 only on || 8.0 || -50 || -75 || -58 || -78 | ||

| + | |- | ||

| + | | All odd on || 12.9 || -40 || -75 || -51.5 || -71 | ||

| + | |- | ||

| + | | All but 8 on || 17 || -36.8 || -72 || -50 || -75 | ||

| + | |- | ||

| + | | Just 8 on || 81.6 || -30.7 || -70 || -53 || -84 | ||

| + | |} | ||

| + | |||

| + | |||

| + | Notice the even harmonics on the unshielded cable. I have a feeling that this is due to the reflections in the line because of improper terminations. Hopefully, this problem will go away when I figure out how to terminate these properly. | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| + | Update: After considering many low-cost solutions for being able to figure out how to measure the LVDS signals accurately, I propose the following solution: | ||

| + | |||

| + | We are fortunate in that the frequency at which we are operating is a fixed one, namely 31 MHz (this solution will also apply equally to the harmonics of a square wave). If we set the oscilloscope to have a high impedance value of 1 MOhm, we can simulate an open-circuit impedance at the test site to the cable if we make the cable length exactly 1/2 of the wavelength (a ballpark figure of the wavelength gives ~6.7m which puts the cable length at ~3.35m). This means that to the DUT it would appear as though we have not really connected anything to the DUT other than the proper LVDS termination. Furthermore, because of high termination of the oscilloscope versus the 50-Ohm impedance of the cable and the nearly matched conditions to the input of the measurement cables, standing waves in the measurement cable should have a minimal amount of "ringing", but the measured value will appear to be approximately twice that actually at the test site. | ||

| + | |||

| + | The downside to this methodology (besides the long cable length) is that sensitivity of the high input impedance is very high compared to the cable length, and the input impedance drops very quickly as the length of the cable moves away from the ideal half wavelength. (This also explains the nasty ringing in the measurements that I made earlier in that the termination impedance was most likely very low input impedance.) To ensure that we can hit the half wavelength mark exactly, we would need to measure and make a special cable for this. To make this cable we could either leave the cable open-ended (or short circuited) and inject a test signal of 31 MHz onto this and another 50-Ohm terminated cable in parallel. When the cable length is exactly correct for the open-ended case, we will see that the test signal will be exactly measured without distortion on a 50-Ohm terminated oscilloscope. This may be somewhat prone to error, and I am also looking at doing a similar thing with a Vector Network Analyzer, if I can get access to one. | ||

| + | |||

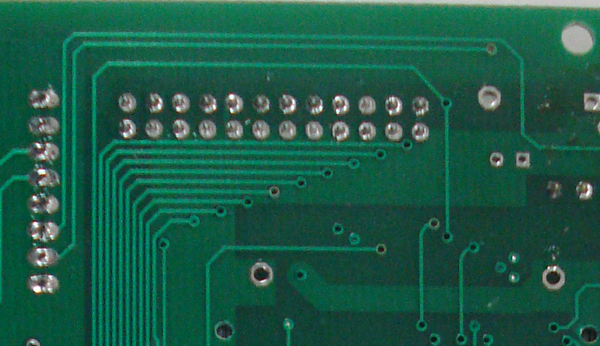

| + | = Circuit Board Dimensions = | ||

| + | |||

| + | For future reference: Circuit Graphic's working panel area is 10" X 16 " (not 10" X 18"). | ||

| + | |||

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |VFAT Breakout Board || HV Dist Bd 1 || HV Dist Bd 2 || Converter Board | ||

| + | |- | ||

| + | | 110 mm X 185 mm || 63 mm X 101 mm || 81 mm X 101 mm || 61 mm X 67 mm | ||

| + | |} | ||

| + | |||

| + | |||

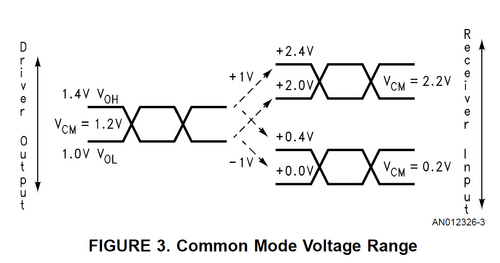

| + | = LVDS Amplifier Research = | ||

| + | |||

| + | From the pictures taken earlier of the LVDS signal at 31 MHz, it would appear that we need an amplifier of a slew rate of at least .5 V/ns = 500 V/us. This may not be doable with an off-the-shelf VFA (voltage feedback amplifier), but it may very well be doable with a CFA (current feedback amplifier) which tend to have a unity-gain frequency of at least two orders of magnitude higher than the VFAs. | ||

| + | |||

| + | One thing that we may have going for us is that we only need to approximately double the voltage going into the cable to get the appropriate value after/before attenuation of the cable. Due to the constant GBP (Gain-Bandwidth Product) nature of most amplifiers this would only half our bandwidth out of the amplifier although I am seeing hints coming from the material I am current studying that CFA's do not quite suffer from the GBP problem that VFAs do. | ||

| + | |||

| + | It may also be difficult to bread-board this circuit due to the very high frequencies involved which tend not to play nicely with the stay capacitances and inductances found in most breadboards. These frequencies are definitely pushing the boundaries of off-the-shelf amplifiers. | ||

| + | |||

| + | = Current v1495 Firmware Versions with Descriptions = | ||

| + | |||

| + | (To use these files one needs to change the type from ".txt" to ."rbf") | ||

| + | |||

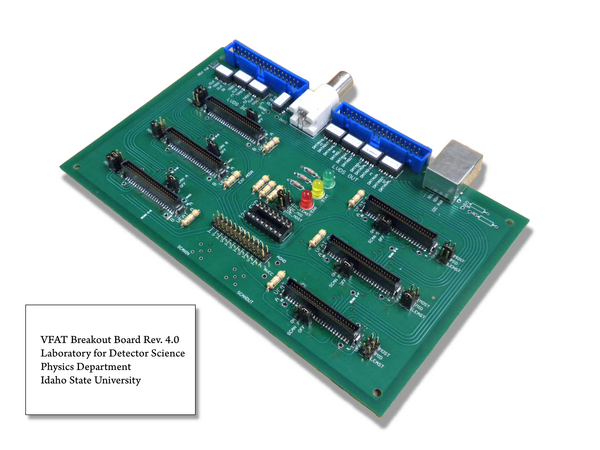

| + | The following firmware version is for Rev 4.1 of the VFAT breakout board. It takes I/O from a single board. The secondary cables are for testing purposes. | ||

| + | |||

| + | [[File:GEMReadout_31MHz_Rev4_1_Test.txt]] | ||

[http://wiki.iac.isu.edu/index.php/User_talk:Parswarr Go back] [[User_talk:Parswarr]] | [http://wiki.iac.isu.edu/index.php/User_talk:Parswarr Go back] [[User_talk:Parswarr]] | ||

| + | |||

| + | |||

| + | =VFAT failure work at CERN= | ||

| + | |||

| + | I traveled to CERN to work with Walter Snoey's group in an effort to determine why I lost 6 VFAT boards when turning sleep mode on and off. | ||

| + | |||

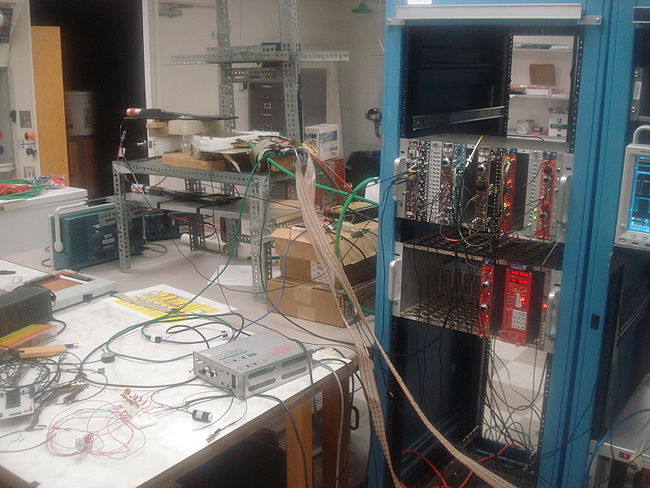

| + | ==8/31/11== | ||

| + | |||

| + | Arrived in the afternoon and setup the ISU hardware in one of Walter's labs. | ||

| + | |||

| + | James Rouet was extremely helpful in getting IP addresses for me as well as electronics, A VME crate, a PM5785 Phillips pulse generator, and a Model 3232 Elind current limited power supply with a voltage range of 32 volts and 3.2 amps. | ||

| + | |||

| + | James also setup a 120 Volt AC outlet so I could use my equipment. | ||

| + | |||

| + | ==9/1/11== | ||

| + | |||

| + | James believes that we should look at how the sense wire is configured on the acopian power supply. He suggested that it should not be grounded to the NIM bin frame but that the wires should meet at the breakout board. | ||

| + | |||

| + | |||

| + | I setup everything so a VFAT card would display the default test pattern. | ||

| + | |||

| + | A VFAT card is pluggedinto the breakout box port "VFAT F" which corresponds to address 112. | ||

| + | |||

| + | The command below will flip the sleep blocking bit | ||

| + | |||

| + | echo "p 112 0 0x01 flip" | ./flipbit.arm | ||

| + | |||

| + | The command below will flip the default test pattern bit | ||

| + | |||

| + | echo "e 112 134 0x10 flip" | ./flipbit.arm | ||

| + | |||

| + | |||

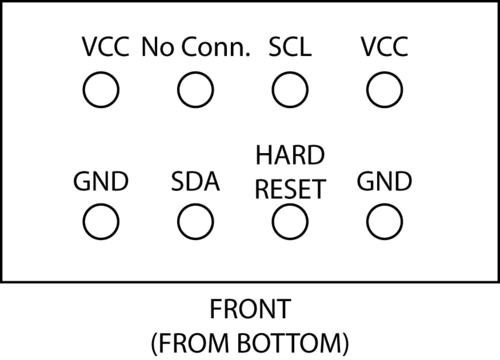

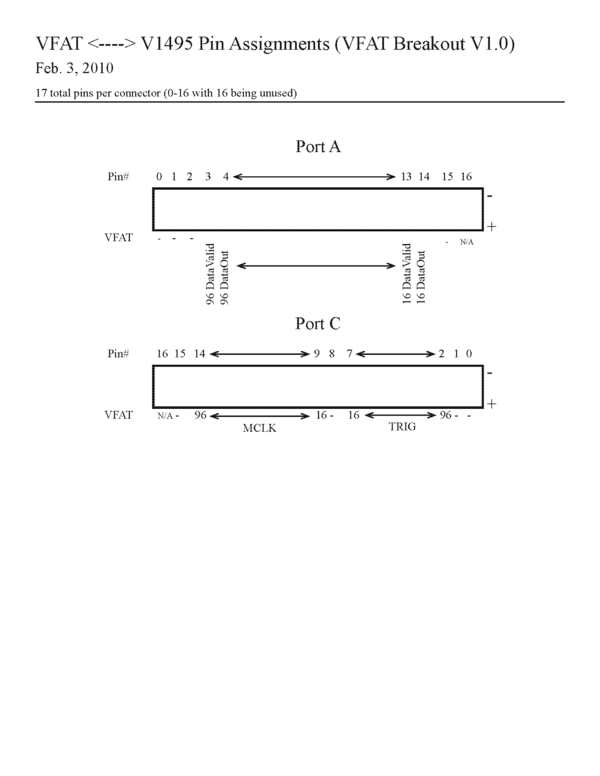

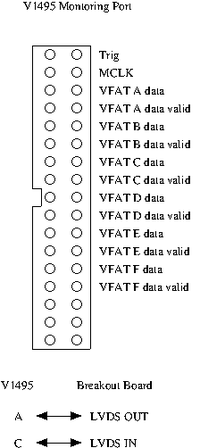

| + | Port A's cable is used to send data From the VFAT to the V1495. Port A's cable goes from the "LVDS out" labeled connector on the breakout board to the V1495 port labeled "A". | ||

| + | |||

| + | Port C's cable toes to the "LVDS IN" port labeled on the Breakout board. | ||

| + | |||

| + | |||

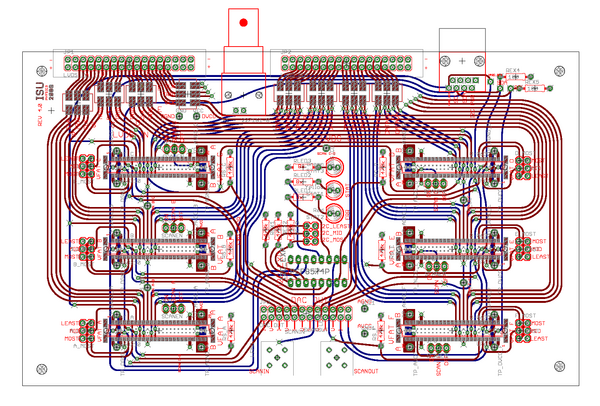

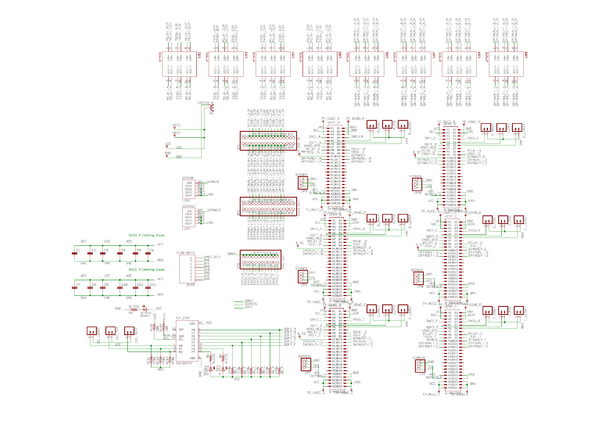

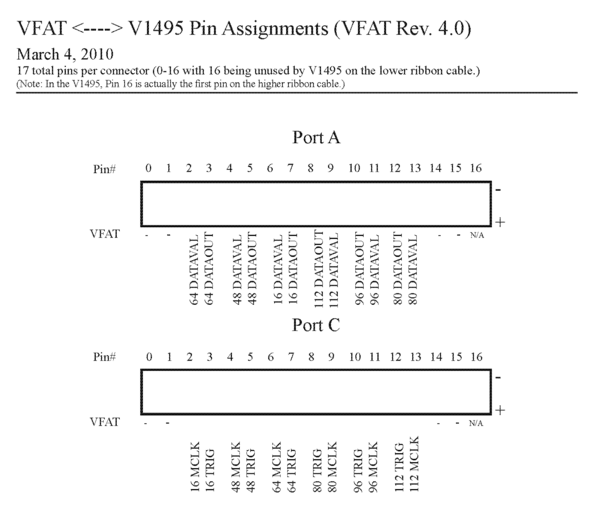

| + | [[File:VFAT2V1495Break1.png|600px]][[File:V1495MonitorPinOuts.png| 200 px]] | ||

| + | |||

| + | Met with Walter and developed the following tests. | ||

| + | |||

| + | 1.) Check the I2C output of the Gumstix | ||

| + | |||

| + | According to | ||

| + | |||

| + | http://www.gumstix.com/store/product_info.php?products_id=184 | ||

| + | |||

| + | the gumstix may be driving the I2C at 3.3 or 5 volts. The VFAT I2C protection diodes clip the signal at 2.5 Volts. | ||

| + | |||

| + | 2.) Check I2C line for damaged chip | ||

| + | |||

| + | Measure the I2C line voltage when talking to a Chip that does not communicate. Perhaps the chip shunts the I2C voltage as a result of being overdriven. The theory is that when going into sleep mode the DC power drop and I2C lines coordinate to over-voltage the chip. Walter has observed that 8 volts can damage the chip. | ||

| + | |||

| + | We may want to install I2C current limiting resistors, TOTEM did this. | ||

| + | |||

| + | 3.) See if Paul has VFAT cards which are not fully functional but still have I2C working. | ||

| + | |||

| + | ==9/2/11== | ||

| + | |||

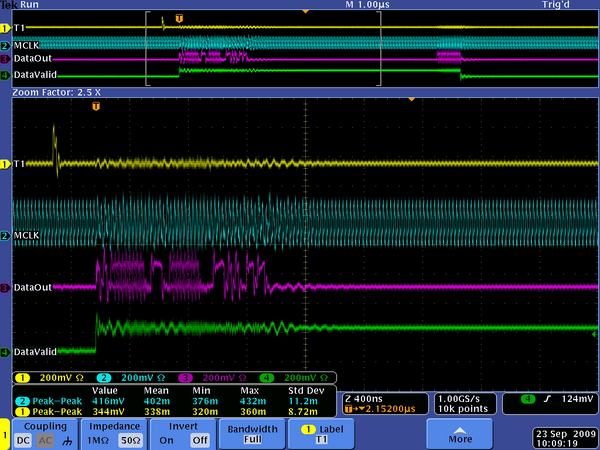

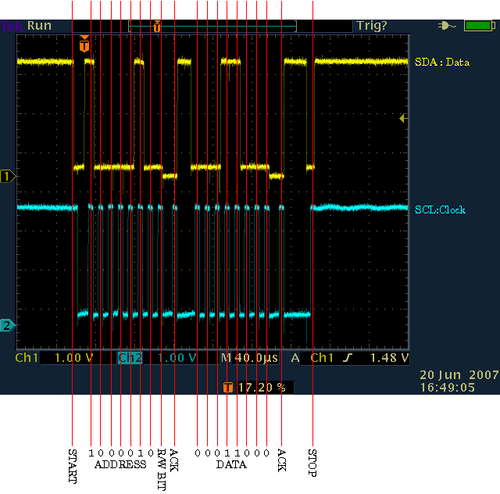

| + | ===I2C Voltage measurements=== | ||

| + | |||

| + | What is the voltage amplitude of the I2C communication signals? 2.5? 3.3? 5.0 V? | ||

| + | |||

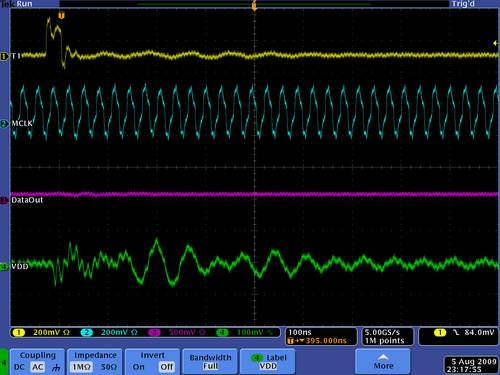

| + | #with no card plugged in I see 3.3 Volts on SCL and SDA. There is a ripple of about 0.2 Volts but always less than 3.3 volts. In other words the voltage is oscillating between 3.0 and 3.3 Volts | ||

| + | #I plugged in a VFAT which has I2C working but no default test pattern. I observed 3.3 Volt swings when I communicate via I2C | ||

| + | #I observed 3.3 Volts when I use the cards with no I2C communication working. | ||

| + | |||

| + | There appears to be a negative swing on the I2C signal that makes the voltage change 4.3 Volts. It lasts for at least 100 ns. | ||

| + | |||

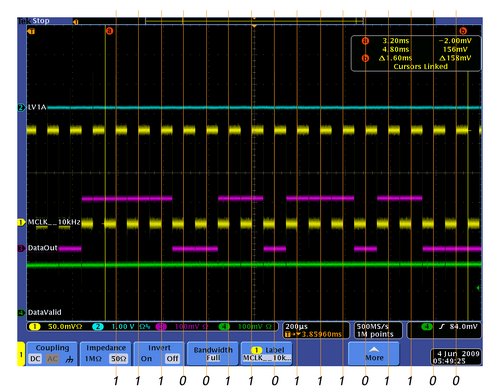

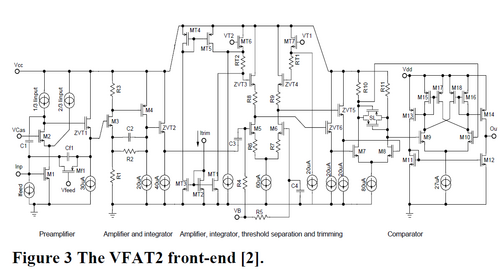

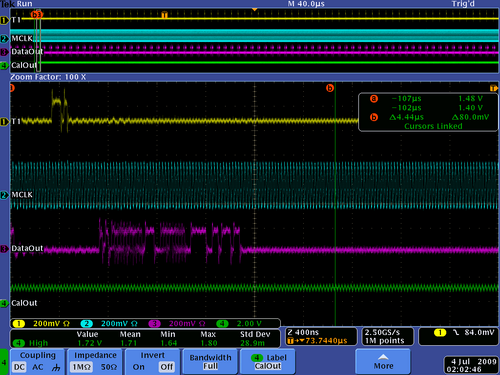

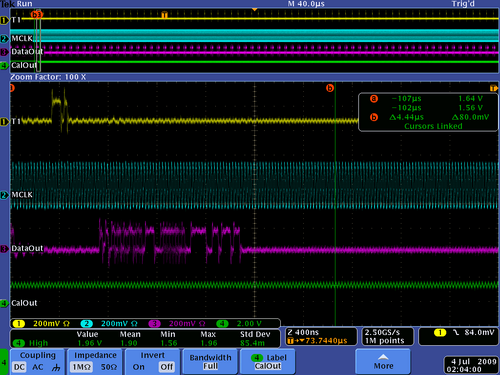

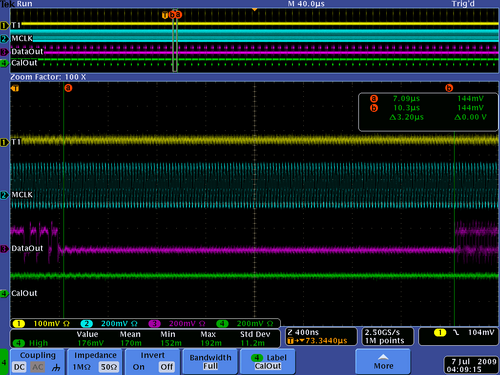

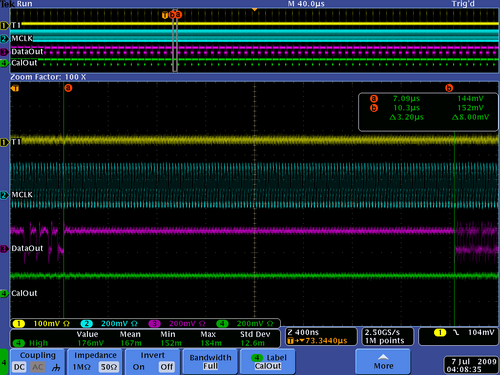

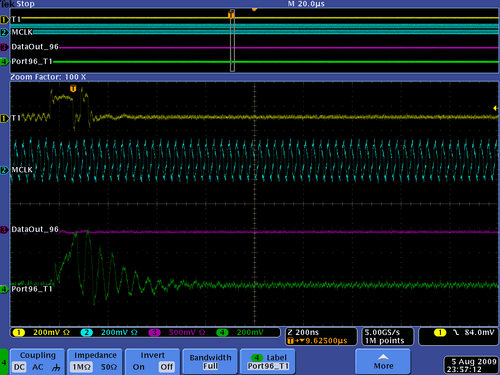

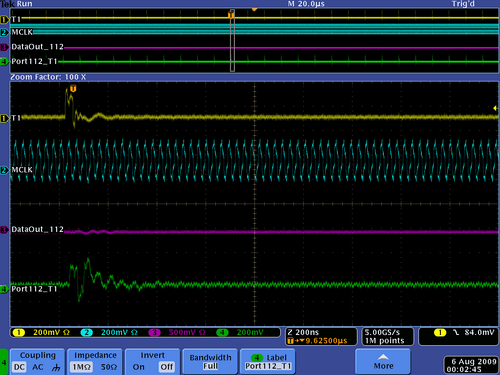

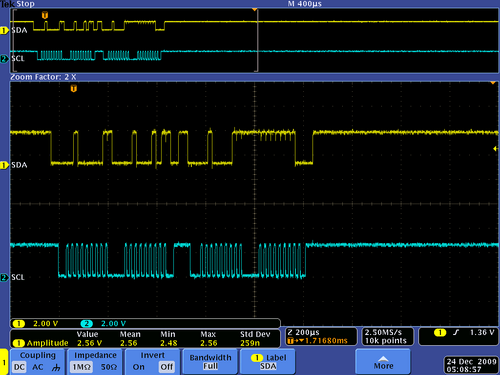

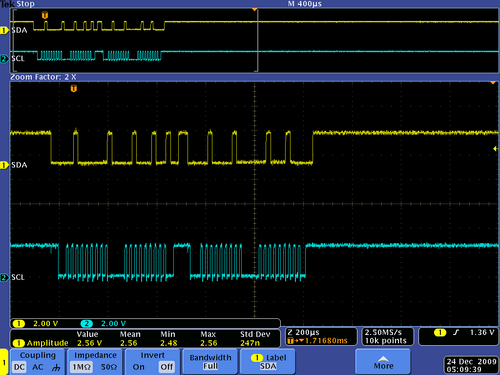

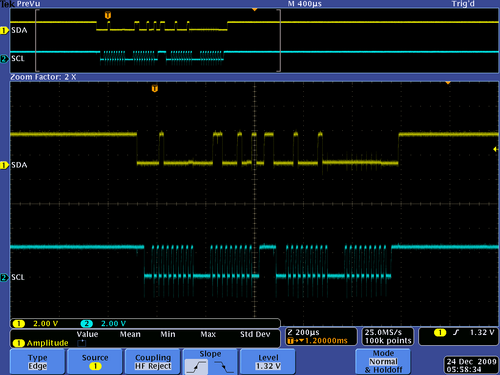

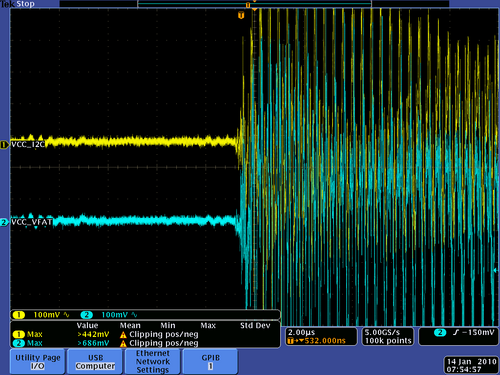

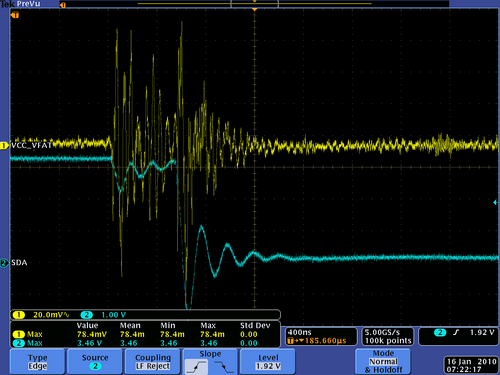

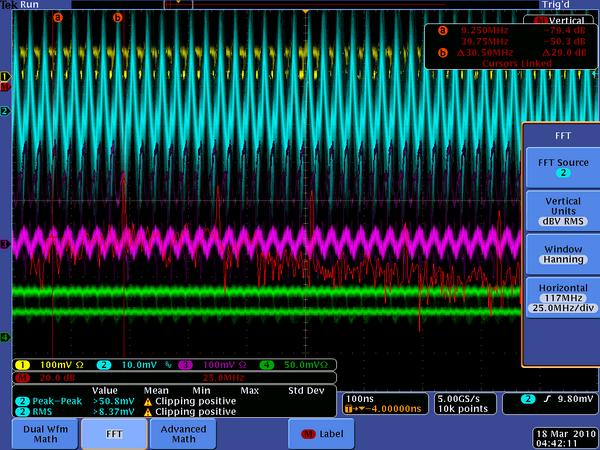

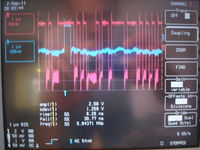

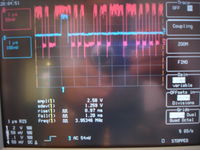

| + | [[File:A09022011_I2CVoltageSwing.png| 200 px]][[File:09022011_I2CVoltageSwing.png| 200 px]][[File:B09022011_I2CVoltageSwing.png| 200 px]] | ||

| + | |||

| + | |||

| + | The images above are observed with and without a VFAT (good or bad) card installed. | ||

| + | |||

| + | |||

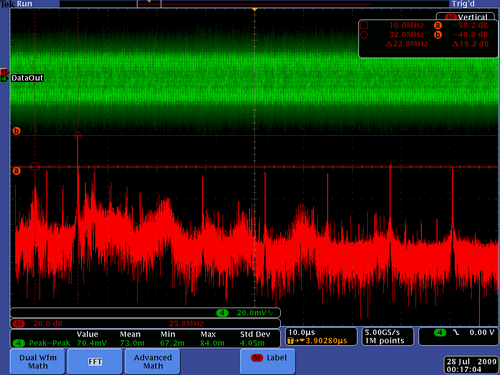

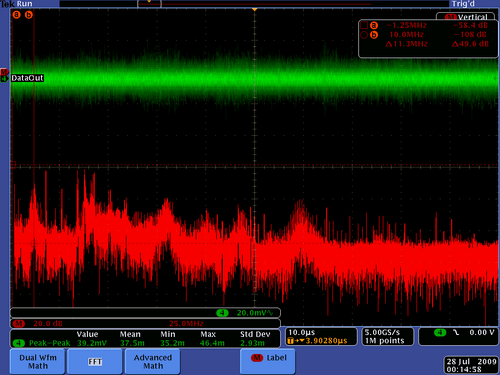

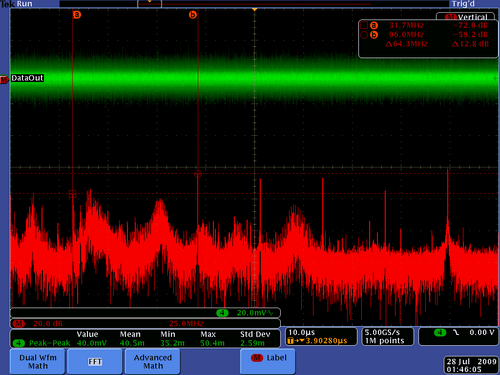

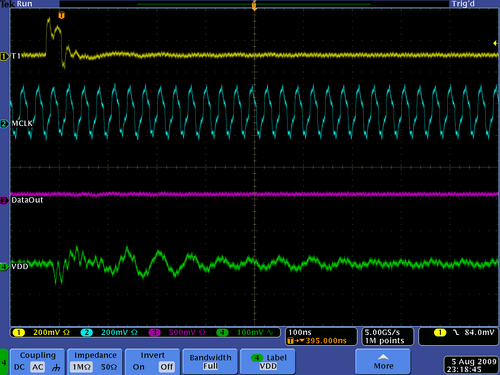

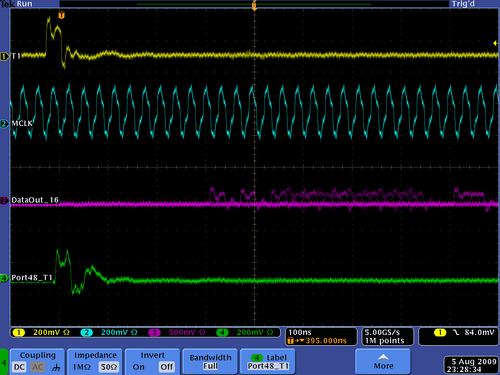

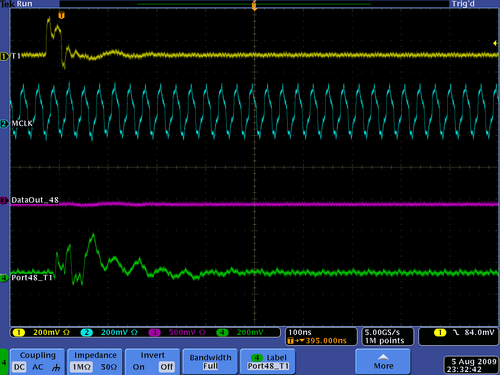

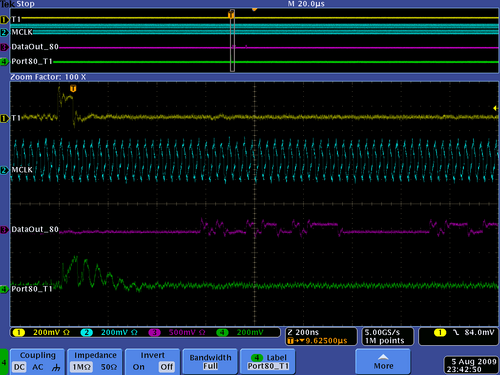

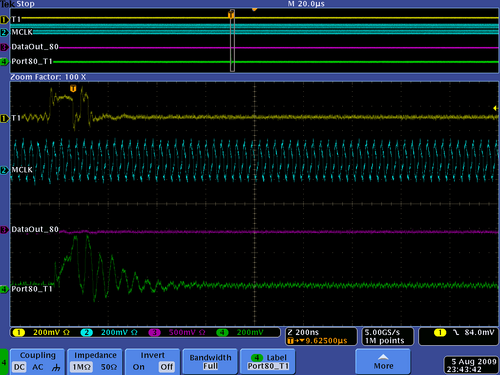

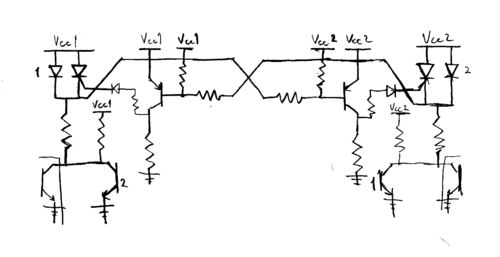

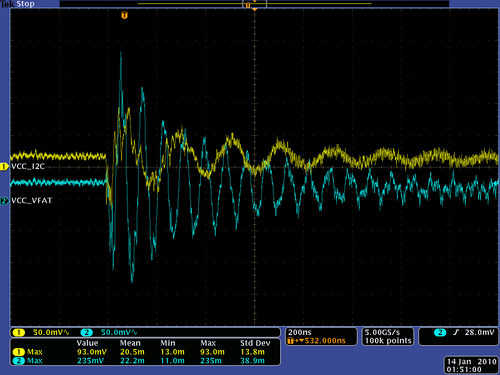

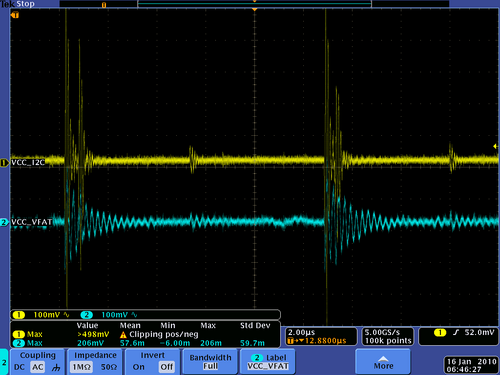

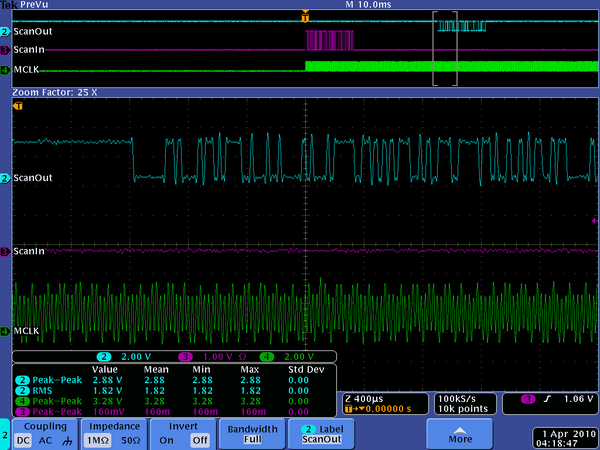

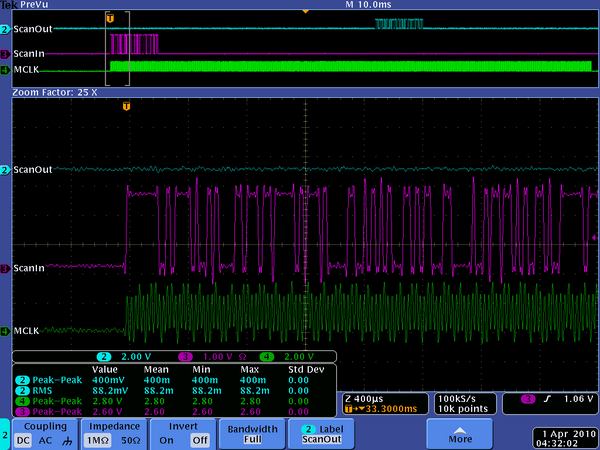

| + | In this series of images you can see how the noise grows depending on the power supply used and the ground. The linear power supply needed to be grounded to the scope. | ||

| + | |||

| + | |||

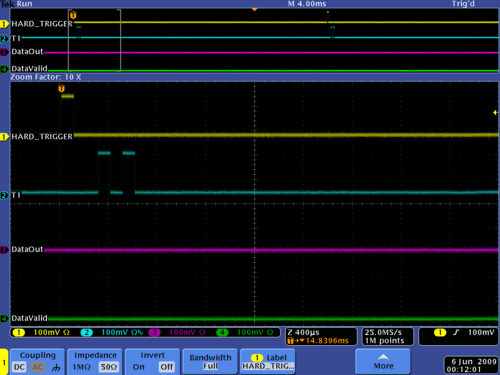

| + | {|border="1" |cellpadding="20" cellspacing="0 | ||

| + | |- | ||

| + | |Trigger Rate||Number of Triggers|| Number of Accept pulses | ||

| + | |- | ||

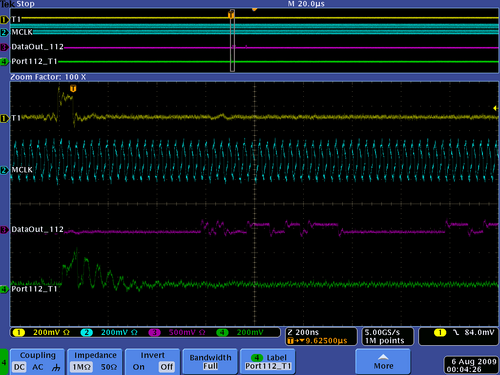

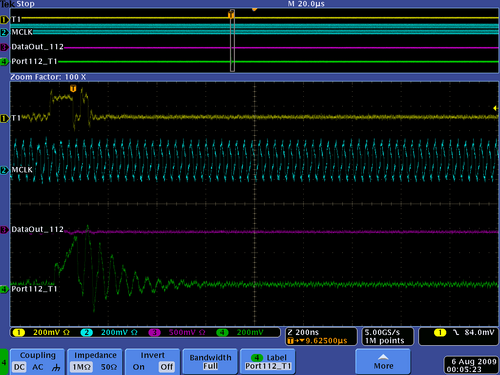

| + | | [[File:09022011_CI2CVoltageSwing.png| 200 px]]|| [[File:09022011_DI2CVoltageSwing.png| 200 px]]|| [[File:09022011_EI2CVoltageSwing.png| 200 px]] | ||

| + | |- | ||

| + | |DATAVALID and DATAOUT when using the linear power supply ungrounded|| Ground the linear power supply. The noise is about 50 mV on the LVDS line || Now using the Acopian power supply. Noise level is about 100 mV | ||

| + | |} | ||

| + | |||

| + | |||

| + | |||

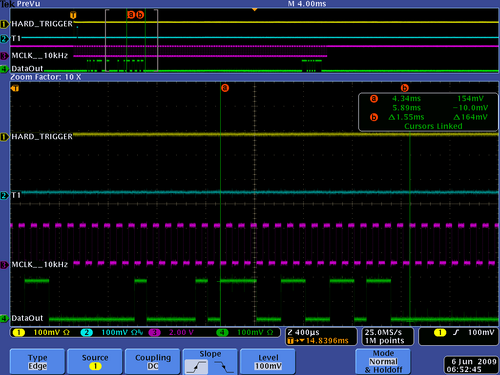

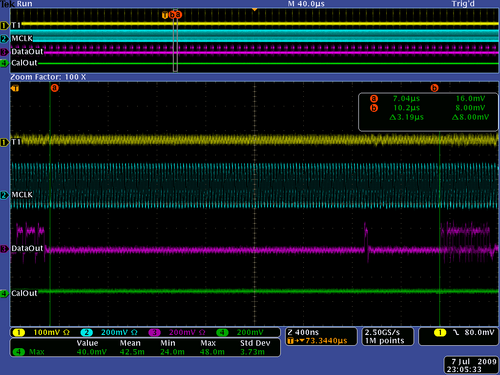

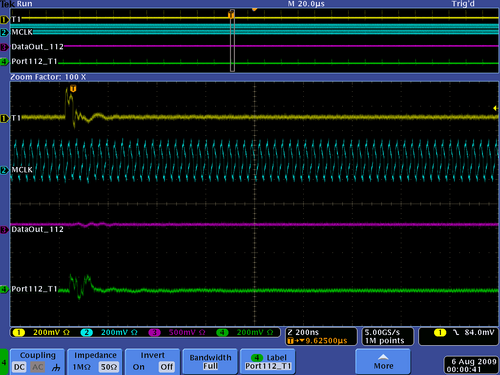

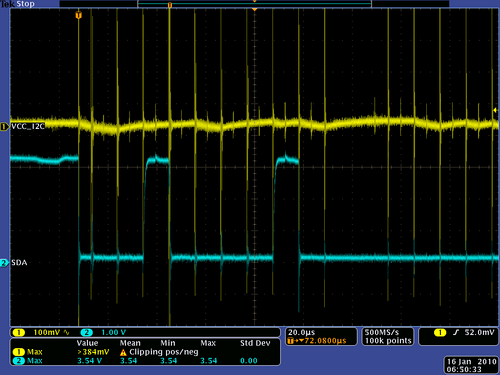

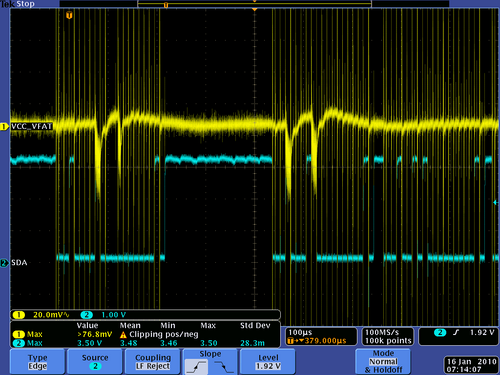

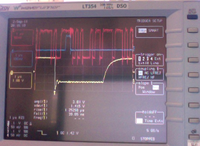

| + | The image below was taken with 6 VFATs installed (4 not working and drawing 0.3 mA each) using my power supply. Channel 1 is an I2C pulse communicating with a VFAT in port 112 (VFAT F). Notice the I2C pulse still swings negative about 1 Volt. Channel 2 is the DATAOUT pulse from the VFAT in port 112. Channel 3 is the DATAVALID pulse from the VFAT in port 112. The VFAT in port 112 is set to output the default test pattern. Notice there is about 100 mV of noise on the LVDS signals. This noise drops to 50 mV when I used the non-switching power supply by elind model 3232. | ||

| + | |||

| + | [[File:09022011_I2CLVDSVoltageSwing.png| 200 px]] | ||

| + | |||

| + | ==TOTEM's power supply== | ||

| + | |||

| + | TTi power supply used in TOTEM, They have one for digital and one for analog chip power. | ||

| + | |||

| + | http://www.ttid.co.uk/products-tti/psu/tsxp-series.htm | ||

| + | |||

| + | I think we can use the Quad version of the power supply below since we only need 2.5 Volts and 1.2 A | ||

| + | |||

| + | http://www.tti-test.com/go/npl/plp-index.htm | ||

| + | |||

| + | == Summary of Changes to make== | ||

| + | |||

| + | #install current limiting resistors so the I2C signal does not exceed 2.5 Volts | ||

| + | #Change power supply BNC connector to be a [http://www.amphenolrf.com/search.asp?sid=4E601C80B2FE17F&N=51 triaxial] one so the ground is isolated from OUT+ and OUT- (S+,S-) | ||

| + | #get a non switching linear power supply with both current and voltage limit settings. Perhaps use a 2.5 volt voltage regulator on its output. Also set power supply current to be limited to 0.2*6 =1.2 Amps | ||

| + | #test the power supply response to VFAT on/offs. A VFAT consumes 0.2 * 2.5 Amp*Volts (Watts) of power at most. When in sleep mode it draws 0.07 A. Measure the voltage output when the VFATs turn on and off to quantify how the power supply modulates the voltage. | ||

| + | |||

| + | |||

| + | ;A broken VFAT has been observed to draw 0.28 Amps compared to the 0.2 amps for a working one turned on and generating a default test pattern. | ||

| + | |||

| + | :ESD protection BNC connector | ||

| + | ;http://www.te.com/catalog/bin/TE.Connect?C=10004&M=PPROP&P=55859,75535&BML=11177,24174,24176,24187,24205,17636,17656&LG=1&PG=1&IDS=465859&N=1 | ||

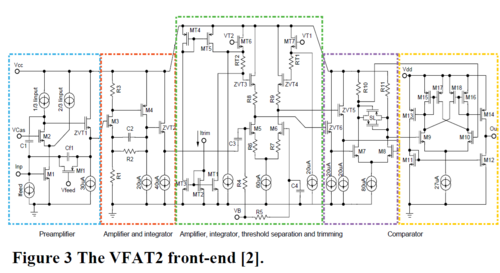

Latest revision as of 19:53, 2 September 2011

This tracks My Daily Progress developing the VFAT readout

VFAT2 Manuals

5/14/09

Firmware

Today we started looking at the VHDL firmware programs from Ben Raydo at JLab. Our goal: To determine what the general description of the firmware program is and determine an outline of its functionality.

Quartus II

Quartus II has a fairly good tutorial for usage. My goal is to complete this tutorial by the end of the week.

I also started to familiarize myself with the VHDL programming language.

5/15/09

Spent vast majority of day learning VHDL syntax.

Spent some time reviewing the GEM Readout Controller Firmware Status

Spent some time reviewing the v1495 instruction manual ( the Quartus II instructions in particular )

Spent some time reviewing the VFAT instruction manual

- Is there a primer somewhere on how to communicate via/with VME?

- How about this http://www.vita.com/vmefaq.html

I need to write down how to get into the DAQ as well as ROC xterm windows.

- Tamuna can show you the above

5/18/09

- From the manual on the VFAT2

- Are we using the Roman Pots or the GEM version for the channel assignments? (I assume the latter.)

GEM version

If I understand the underlying functionality of the output of the VFAT2 then the basic idea is that it transfers the hit data from SRAM1 to SRAM2 as soon as there is a LV1A signal (100) sent to the VFAT2 via the "T1" line (after the latency time programmed into the Latency Register with a default setting of 6.4us).

I thought the max latency is 6.4 us and the default is zero

Once data is transferred from SRAM1 to SRAM2 it immediately starts outputing the information on "DataOut" at the "MCLK" rate of 40Mhz (I assume to be ultimately governed by the v1495). Valid data can be found on the "DataOut" line as long as the "DataValid" line is high. Thus the LV1A signal on "T1" followed by a transition to high on the "DataValid" line should set off the v1495 data capturing routine. Data is clocked out in FIFO order if more LV1A signals are sent to the VFAT2 before all of the data has been transferred out of the VFAT2.

I am unclear if the V1495 firmware is programmed to begin a read when the LV1A trigger transitions or when DataValid transition. I think it should be when DataValid transitions.

Tamuna and I tried to log onto the ROC from scratch, but the ROC keeps saying that it can't find some boot file. I started to look through the ROC file on Dr. Forest's wiki pages, but I do not find this to be a straightforward process of rebooting the ROC. The following entry is related, and it may be helpful.

- Would it be useful to purchase the VMEbus Handbook, 4th Edition by Wade Peterson? I have personally never worked with such a complicated system with so few written resources as the VME system. I have now read quite a bit about the history of the VME system, and yet I have yet to be able to read anything on how to actually use this system. How does one begin to even crack into this system? It is a full-blown microcontroller complete with its own operating system including the complete gamut of hardware and software.

- Where did we get this Quartus II software from and why has the 30-day trial period run out? This may be making it so I cannot compile a project and get it loaded into the v1495 via the ROC. I get this impression from the fact that when I attempt to compile the project only one error comes up and that is that the 30-day evaluation period has expired. Do we have a license for it somewhere?

Licenses are free. see http://wiki.iac.isu.edu/index.php/Qweak_V1495_FPGA_Programming for the download page

5/19/09

Tamuna, Brian, and I worked on trying to fix the MVME6100 but to no avail. I think it's actually getting worse the more we try to get it working. We may need to wait until Dr. Forest returns before attempting to fix it. I plan on reading some more information that I found on the whole VME system as well as the MVME6100 and its associated OS, VXWorks, which is apparently used in a lot more applications than I was previously aware.

I was able to contact Ben Raydo. Thankfully he had given me quite a few suggestions on how to get started with the v1495 side of this project. I am sifting through the information he has given me.

I have found much more information on the VME system today including information on the MVME6100 (as already stated) as well as other documentation.

5/20/09

I had to brush up a bit on Verilog to figure out what was going on in the v1495usr_hal.vqm file because it is written in Verilog HDL. I have added its description above.

By whatever mystical powers the ROC is apparently now working again. I would however like to know exactly what happened to get it working.

I still need a license for Quartus II in order to continue working directly on the v1495. However, I did spend a great deal of time reading how to use the MVME6100 as well as the v1495.

5/21/09

I was able to figure out how to get the license for Quartus II and to compile an .rgb file that can be loaded into the v1495 USER FPGA. I was not aware before that we already had a completely working firmware version for the v1495 USER FPGA.

- In looking through the VHDL code to figure out how it works I have made the following discoveries

- The code in GEMReadout.vhd governs the behavior of the GEMReadout component.

- Code governing the G0 (Gin(0)) and G1 (Gin(1)) Inputs

- In GEMReadout.vhd the signal GIN(1) gets loaded into HARD_TRIGGER. HARD_TRIGGER then gets loaded into the HARD_TRIGGER of the GEMTrigger component as well as the HARD_TRIGGER of a GEMTxChannel component. Thus far I am unclear what is done with this HARD_TRIGGER signal for these components. I will figure this out on Friday, hopefully.

- Still in GEMReadout.vhd the GIN(0) signal gets loaded into the inclk0 value of the PLLBlock component. In PLLBlock.vhd (which governs the behavior of the PLLBlock component), this c0 signal eventually ends up being connected to clk(0) for the altpll component. The altpll component appears to be a predefined cell in Quartus II. I hypothesize that this component is just a pll with user-defined settings. Hopefully on Friday I can find some documentation on this component to figure out exactly how it works. Thus in GEMReadout.vhd we put in our original signal G0 and get out a locked version on PLLCLK.

- This appears to be in GEMReadout.vhd where the process trigger PLLCLK is generated. All other components that take this value in on one of its ports has it as an input rather than an output.

- nLBRES is a system-wide asyncronous reset

- LCKL is a local bus clock

- I cannot figure out where this is being generated because I lose its trail into the v1495usr_hal.vqm file going to

5/22/09

altpll is indeed an Altera Megafunction. inclk0 is the reference clock to the output clocks c0 and c1. c0 is exactly in phase with inclk0 which appears to be running at a nominal frequency of 32Mhz which as stated before ultimately ends up being the PLLCLK signal in the GEMReadout block. c1 is a phase shifted version of inclk0. Although it states that this ends up being PLLCLK_90 in GEMReadout.vhd, it is actually 180 of phase shift, i.e. an inverted clock pulse. I don't know why it was given this name since it doesn't make sense.

These calculation can be done using the input parameters to the altpll plock in the PLLBlock.vhd code from the following lines.

altpll_component : altpll GENERIC MAP (

- clk0_divide_by => 1,

- clk0_duty_cycle => 50,

- clk0_multiply_by => 1,

- clk0_phase_shift => "0",

- clk1_divide_by => 1,

- clk1_duty_cycle => 50,

- clk1_multiply_by => 1,

- ;clk1_phase_shift => "15625", <-- This is the phase shift in ps.

- compensate_clock => "CLK0",

- ;inclk0_input_frequency => 31250, <-- This is the input frequency given as the period in ps.

- intended_device_family => "Cyclone",

- invalid_lock_multiplier => 5,

- lpm_hint => "CBX_MODULE_PREFIX=PLLBlock",

- lpm_type => "altpll",

- operation_mode => "NORMAL",

The units for the frequency cannot be found in the literature. The way I figured this out was to create an altpll Megafunction block with a strange frequency. After it generated the VHDL code for the megafunction I was able to see that the output of the inclk0_input_frequency was in ps.

5/26/09

- On the question of I/O Levels.

- There are two different pin voltage levels to consider here: the I/O levels coming into the board and the I/O levels of the Cyclone chip.

- The input levels going into G0 and G1 are LVTTL (3.3V). This information, as well as the pin output assignments, are located under the menu "Assignments->Pins" in the Quartus II program.

- This information is part of the project that was created for this design. What that means is that it is not enough to just import the text files for this project and compile it. One needs the project file ".qfp" which has all of the proper pin assignments including location and levels.

- The I/O levels going into and out of the v1495 is much more difficult to ascertain. The following is an example from the GEMReadout.vhd file which programs the levels as well as whether a pin is input or output.

- The nOEx signals are whether or not a bidirectional pin is configured as an output or an input. A logic level "0" is an input.

- The SELG signals are whether or not a pin is TTL or NIM on the G I/Os. A logic level "0" indicates that this is a TTL level.

- The preceeding was gleaned from the v1495usr_demo project that can be downloaded for free from CAEN. There must be some hardware external to the Cyclone chip but still on the v1495 that selects these settings.

- Thus far I have not found the documentation that demostrates how this is actually done. Like I said before, at this point I have only been able to glean the information from the v1495user_demo project. Therefore, it would not surprise me if this information was somewhat faulty.

The following code was used to see if I could turn off the Red LED:

RED_PULSE <= SYS_RESET; GREEN_PULSE <= HEART_BEAT_CNT(25); -- SYS_RESET <= not nLBRES or not PLL_LOCK;

After resetting the VME crate, it appears to have worked. I was previously under the impression that one did not have to bump the power on the v1495 to get it to use its new firmware. I will have to explore this.

The rate at which the Green LED blinks is based off of the following code out of GEMReadout.vhd.

signal HEART_BEAT_CNT : std_logic_vector(25 downto 0);

process(LCLK, nLBRES) begin if nLBRES = '0' then HEART_BEAT_CNT <= (others => '0'); elsif rising_edge(LCLK) then HEART_BEAT_CNT <= HEART_BEAT_CNT + 1; end if; end process;

Basically what these lines of code are saying is that HEART_BEAT_CNT is a 26-bit register that originally gets set to '0'. On either a change in LCLK or nLBRES and if LCLK is a rising edge, then the HEART_BEAT_CNT gets incremented by one. From the lines of code shown before this block, GREEN_PULSE is set if the MSB of HEART_BEAT_CNT is set. Therefore, the Green LED should blink at a 50% duty cycle of 2^(25)*(20Mhz)^(-1) = 3.35 s for a 20MHz PLL frequency (i.e. on for 1.67s, off for 1.67 s).

Tomorrow I will need to determine what the signals "SYS_RESET, nLBRES, and PLL_LOCK" actually are and what they mean. As I have alluded to before, I loose the trail for many of these signals at the Cyclone package level and can only infer what their actual purposes are at this point based on the code from the GEMReadout as well as the v1495usr_demo.

5/27/09

I then doubled the PLL frequency to see if it would double the rate at which the LED was blinking. It worked.

- What this means is that the LCLK signal is somehow internal to the chip and has nothing to do with the signal that is being injected on G0.

I then changed the code back on the RED LED to see if I could restore the RED LED status with the new faster GREEN LED rate.

- This worked as well.

I attempted to change the firmware back to the original 20MHz configuration, but it does not seem to have slowed down the blinking GREEN LED at all. I am wondering if the 20MHz version was somehow corrupted. I will recompile and send this over to see if I can slow the blinking GREEN LED down.

Note: This is because the Green LED depends on the system "LCLK" rather than the "PLLCLK" which is supposed to be a reflected version of the G0 input.

The following multipin connector settings can be found in the v1495 user manual and show explicitly where the proper pin connections can be made.

For my last item of the day I attempted to reset the Green LED to blink with "PLLCLK" rather than "LCLK." This only led to the Green LED remaining solid. This, as well as our previously failed attempts to lock with the frequency of the PLL, seems to suggest that the v1495 is not even registering the G0 input.

5/28/09

Today I attempted to get the LED to blink to the LCLK rather than the PLLCLK. It did not work.

Later I attempted to get C(1) to output the LCLK, which drives the Green LED, rather than PLLCLK_90. This also did not work.

Both of these seem to suggest that the Cyclone chip is somehow to communicating to the I/O ports on the v1495.

5/29/09

I was able to fix the firmware uploading code so that the board now resets with the new firmware loaded as well as actually exiting the program. I did this by making the following changes to the functions in v1495.c.

int

v1495reload()

{

volatile V1495 *v1495 = (V1495 *)0xfa510000;

int

v1495reload(unsigned int baseaddr)

{

volatile V1495 *v1495 = (V1495 *)baseaddr;

int

v1495firmware(unsigned int baseaddr, char *filename, int page, int user_vme)

{

.

.

.

v1495reload(baseaddr); // This loads the proper base address it for refresh

return(0); // This used to be an exit(0) command thus never allowing the program to exit properly.

// I suspect that exit(0) is not a VXWorks function.