Difference between revisions of "VFAT powered on and responding to I2C"

Jump to navigation

Jump to search

| Line 1: | Line 1: | ||

[[Image:i2c_scope.png]] | [[Image:i2c_scope.png]] | ||

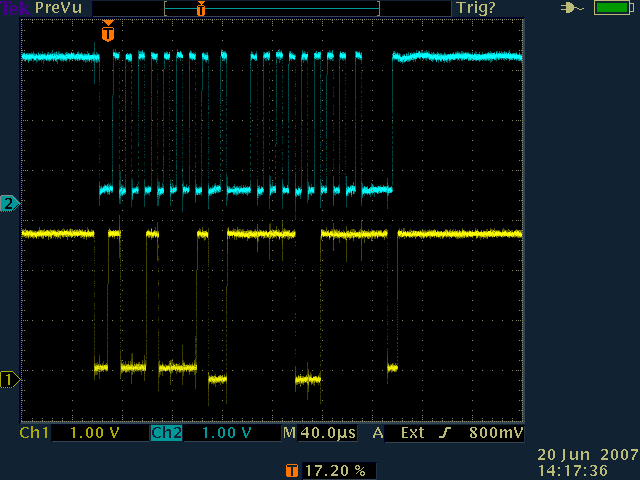

| − | This is a picture of an i2c read operation on the VFAT board. The VFAT is on addresses 0x40 thru 0x48. This trace is reading address 0x48, which is the first part of the ChipID. This value is F3 for this chip. | + | This is a picture of an i2c read operation on the VFAT board. |

| + | The controller starts communication with the device by giving a start signal and then the adress, which is 0x48 and corresponds to the first part of the ChipID. The chip then responds with the return byte, which is 0xF3 for this particular device. Finally the controll | ||

| + | |||

| + | The VFAT is on addresses 0x40 thru 0x48. This trace is reading address 0x48, which is the first part of the ChipID. This value is F3 for this chip. | ||

Revision as of 21:01, 20 June 2007

This is a picture of an i2c read operation on the VFAT board. The controller starts communication with the device by giving a start signal and then the adress, which is 0x48 and corresponds to the first part of the ChipID. The chip then responds with the return byte, which is 0xF3 for this particular device. Finally the controll

The VFAT is on addresses 0x40 thru 0x48. This trace is reading address 0x48, which is the first part of the ChipID. This value is F3 for this chip.