Difference between revisions of "CAEN V792 ADC"

| Line 117: | Line 117: | ||

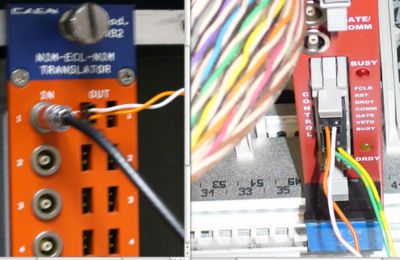

= ECL input polarity= | = ECL input polarity= | ||

==Control lines== | ==Control lines== | ||

| − | [[Image:ECL-QDC_FSTCLR.jpg]] | + | [[Image:ECL-QDC_FSTCLR.jpg | 400 px]] |

Revision as of 18:53, 25 February 2008

Module address

Rotary dials

The rotary dials for the address were set by the factory to be 32 bit addressing with "e" and "e" on the last dials.

We would like to use 24 bit addressing so lets set the first two dials to "ee". The last two dials should also be set to something non-zero in order to permit 32 bit addressing. The MVME-6100 board only has a small amount of 32 bit VME addressing space mapped to the MVME's address space.

VME CPU

A24 0x000000-0xffffff 0x90000000-0x90ffffff

A32 0x08000000-0x11ffffff 0x80000000-0x89ffffff

If you set the last two dials to 0 8 then the addressing will look like

c792Init 0xee0000 (for A24 addressing)

or

c792Init 0x08ee0000 (for A32 addressing)

Data banks

The ADC module library will send the entire block over unless you set the ADC for specification.

Below is shown the data structure for Multi-Event Buffer. The data is organized in events[1]. The header, which contains the crate number and the number of converted channels(the second row in the table), the data words - the number of the channel, the Under-Threshold (UN) bit, the Overflow (OV) bit and

the 12-bit converted value(ADC COUNTS) and event counter is in The End of Block.

- The Header

The bits[26..24] - shows the word type(010 - header);

The bits[23..16] - the crate number;

The bits[13...8] - the memorized channel number.

- The data words

The bits[26..24] - the type of word (000 - datum);

The bits[21..16] - the data output channel number;

The bit[13] - the underthreshold;

The bit[12] - the overflow;

The bits[11...0] - the 12 bit converted data.

- The End of Block(EOB)

The bits[26..24] - identification of the word type(100 - EOB);

The bits[23..0] - the event counter value.

| 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 1 | 0 | CRATE NUMBER | 0 | 0 | MEM. CHANNELS(2) | ||||||||||||||||||||

| 0 | 0 | 0 | CHANNEL(2) | UN | OV | ADC COUNTS | ||||||||||||||||||||

| 0 | 0 | 0 | CHANNEL(5) | UN | OV | ADC COUNTS | ||||||||||||||||||||

| 1 | 0 | 0 | EVENT COUNTER(m) | |||||||||||||||||||||||

| 0 | 1 | 0 | CRATE NUMBER | 0 | 0 | MEM. CHANNELS(3) | ||||||||||||||||||||

| 0 | 0 | 0 | CHANNEL(0) | UN | OV | ADC COUNTS | ||||||||||||||||||||

| 0 | 0 | 0 | CHANNEL(17) | UN | OV | ADC COUNTS | ||||||||||||||||||||

| 0 | 0 | 0 | CHANNEL(3) | UN | OV | ADC COUNTS | ||||||||||||||||||||

| 1 | 0 | 0 | EVENT COUNTER(m+3) | |||||||||||||||||||||||

Assuming we read all 32 channels then the data block will look like

ADC1: Crate #=0 Ch data Hex 0 3896 f8005f38 16 3896 f8105f38 1 3896 f8015f38 17 3896 f8115f38 2 3896 f8025f38 18 3896 f8125f38 3 3896 f8035f38 19 3896 f8135f38 4 3896 f8045f38 20 3896 f8145f38 5 3896 f8055f38 21 3896 f8155f38 6 3896 f8065f38 22 3896 f8165f38 7 3896 f8075f38 23 3896 f8175f38 8 3896 f8085f38 24 3896 f8185f38 9 3896 f8095f38 25 3896 f8195f38 10 3896 f80a5f38 26 3896 f81a5f38 11 3896 f80b5f38 27 3896 f81b5f38 12 3896 f80c5f38 28 3896 f81c5f38 13 3896 f80d5f38 29 3896 f81d5f38 14 3896 f80e5f38 30 3896 f81e5f38 15 3896 f80f5f38 31 3896 f81f5f38 Event Counter=46=0xfc00002e

command used to compile library

v792 >ccppc -fno-builtin -fno-for-scope -fstrength-reduce -mlongcall -mcpu=604 -DCPU=PPC604 -DVXWORKS -D_GNU_TOOL -DVXWORKSPPC -I/usr/local/coda/2.5/common/include -I../h -c -o v792Lib.o caen792Lib.c