Difference between revisions of "A W CAA apparatus"

| Line 43: | Line 43: | ||

=Signal Processing= | =Signal Processing= | ||

| + | |||

| + | ==Analog output== | ||

| + | |||

| + | describe the analog pulse shapes from each detector. be specific on time and voltage and sign… | ||

| + | |||

==Analog amplification== | ==Analog amplification== | ||

Revision as of 20:14, 16 October 2014

Detectors

HpGe

Type (npn or pnp): Ortec

Model #: SGD-GEM-50180P-S

Crystal dimensions: active diameter 65 mm (6.5 cm)

Operating voltage: 4600 V

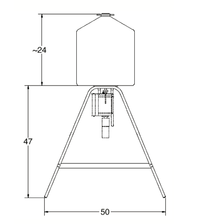

A high-purity germanium (HpGe) detector is the first of two detectors used in for our coincidence set-up. HpGe detectors have an energy resolution of 1 keV. We used a p-type germanium from Ortec model SGD-GEM-50180P-S with an active crystal diameter of 65 mm. We operated the detector at its bias voltage of 4600 V using the SMART interface computer software. In order to reduce thermal excitations of valence electrons so only a gamma ray interaction is detected, the detector must be cooled to liquid nitrogen temperatures. FigureXX.YY shows the detector with a dewar attached that kept the detector cool for at least one week before additional nitrogen was required.

NaI

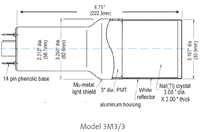

Type: Bicron

Model #: 3M3/3

Crystal dimensions: inches ( cm)

Operating voltage: -1000 V

Add sentence on how NaI detector works.

The second detector employed in our coincidence set-up was a Sodium Iodide (NaI) detector. We used a Bicron model 3M3/3 detector with a inch crystal. The PMT voltage was set at -1000 V. A picture of the detector and its diagram can be seen on figures XX.YY and XX.YY.

Geometry

Samples were positioned on top of polyethylene blocks. Polyethylene replaced cement blocks to reduce the background from the cement blocks. The HpGe detector was suspended from a dewar 9.5 cm above the sample. The NaI detector is perpendicular to the HpGe detector and 6.7 cm from the sample. The NaI detector was shielded using two standard (2x4x8 inch) Pb bricks. A drawing of the apparatus is shown in Figure XX.YY.

Signal Processing

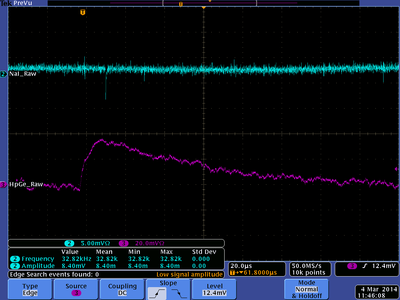

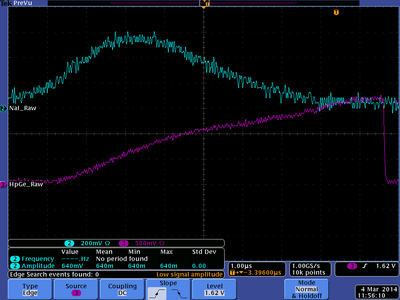

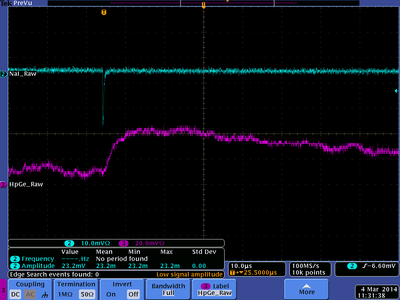

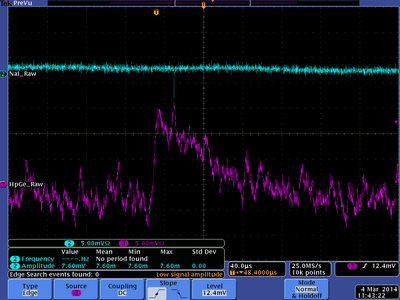

Analog output

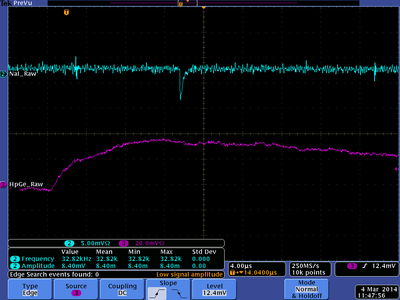

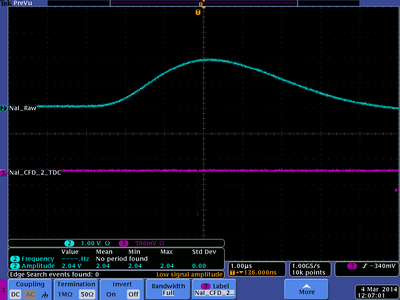

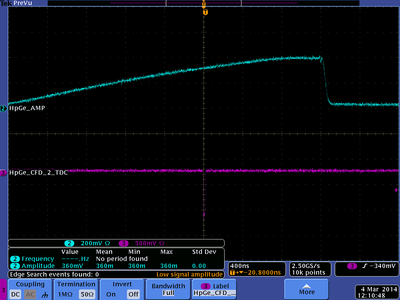

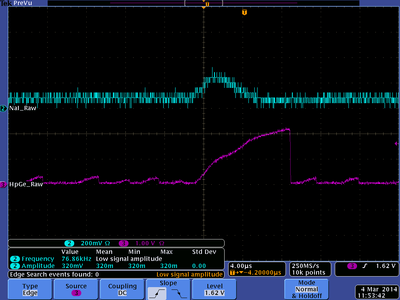

describe the analog pulse shapes from each detector. be specific on time and voltage and sign…

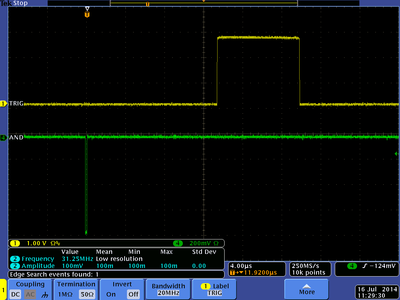

Analog amplification

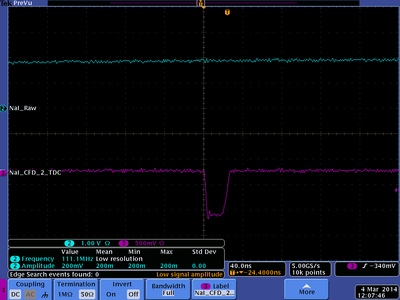

Discrimination

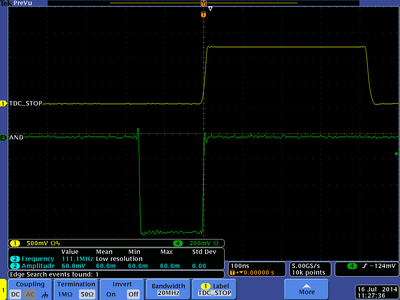

Signal Trigger logic

Insert you paragraphs describing the apparatus

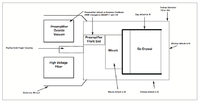

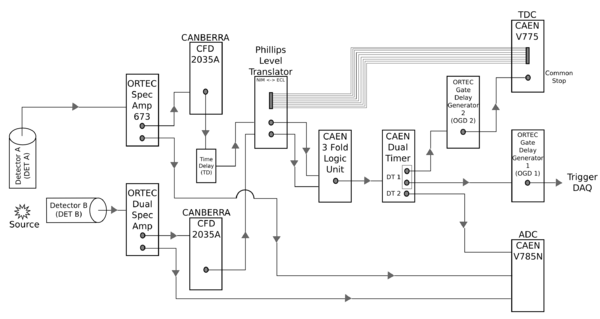

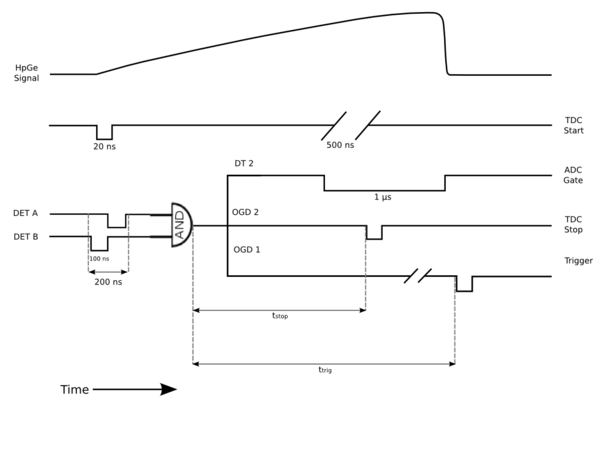

The coincidence counting set-up and modules path are as follows. A source is set atop a base constructed of hydrogen dense blocks. These were chosen to reduce the number of background energy spikes detected. The source is placed an equal distance from decorator A and detector B.

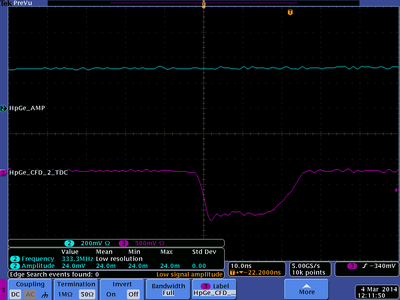

Detector A is positioned directly above the source. A high-purity germanium detector is being utilized for this set-up. The one outgoing signal enters a ORTEC 673 Spectroscopy Amplifier and the outgoing signal then passes through a CANBERRA CFD 2035A. The signal can then enter an optional CAEN CFD to produce a time delay, or can pass directly into a channel (1) of the Level Translator. The second outgoing signal from the Spec Amp goes to a peak sensing CAEN V785N. The output from this module goes to the DAQ.

Perpendicular from detector A and placed an equal distance from the source is detector B. This detector can either be a NaI-3 or a germanium detector depending on the source being counted. Detector B’s signal goes to a Post Amplifier and one outgoing signal goes to the above mentioned CAEN V785N and also to the DAQ. The second signal enters a CANBERRA CFD 2035A. The outgoing signal goes to a different channel (4) of the same Level Translator. A ribbon cable on the Level Translator module goes to a Time-to-Digital Converter (TDC) CAEN V775 that is operating in common start mode.

Both channels (1 and 4) of the Level Translator outgoing signal pass to a 3-fold Logic Unit which is used in both OR mode and AND mode to see coincidence lines. This data is collected in the Trig DAQ.