Difference between revisions of "HRRLrun 3-22-26-2010"

| Line 99: | Line 99: | ||

Then, study how the hits in the VFAT change with latency by changing the latency between values of 6-12. | Then, study how the hits in the VFAT change with latency by changing the latency between values of 6-12. | ||

| + | |||

| + | end the day with everything in time | ||

=3/26/10= | =3/26/10= | ||

Revision as of 03:33, 25 March 2010

HRRL run on March 22-26 2010

Preliminary setup

3/17/10

Install detector infrastructure to mount 2 Drift chambers, 2 Scintillators and 1 GEM on a translator table.

Install collimation

3/18/10

Install all detectors and associated electronics (power supplies, cabling, gas lines,...)

Timing concept

There are 3 modules to be readout; an ADC, a TDC, and the V1495.

The ADC requires a gate defining the integration interval of the pulse. The TDC requires a start pulse to begin the TDC clock and a stop pulse to stop the TDC clock. The V1495 requires a trigger pulse to tell it there is data coming from the VFATs.

The ADC and TDC will be run so they get pulses every time there is a RF pulse. The data are only recorded though if there is a coincidence pulse telling them to keep the data. Otherewise the ADC and TDC will throw the data away.

ADC timing pulse

The linear output of the 3 Fold coincidence module is generated whenever there is an RF pulse from the accelerator and is sent to the 2-channel dual timer. The top channel of the dual timer receives the 3-FOld coincidence linear output and its delayed output is send to the bottom channel of the Dual timer. The bottom of the Dual timer will be used to set the gate width. So use the top channel to adjust the gate such that it is in time with the FC output pulse. Then adjust the bottom channel so the with of the gate integrate over the desired part of the FC output.

TDC timing

3/19/10

install DAQ system and associated readout electronics.

Check channels in histograms

Coincidence: Coincidence between Accelerator's RF pulse generator, and several PMTs

TDC start: Accelerator RF pulse generator. TDC stop: 2 DC, 1 GEM trigout, 4 PMTs

ADC: all FC channels from Accelerator ribbon cable. ADC gate: Create timing gate using scope when accelerator

V1495: Trigger pulse from coincidence logic above

3/22/10

Final day for completing system checks

3/23/10

1pm - 5pm: Tune beam for low and high current

Set the timing for the ADC gate and the ADC FAST CLEAR

3/24/10

FC

The FC was readout using CODA and the CAEN ADC 792. There were 3 hot channels represent 3 out of the 16 2" bricks stacked up at the end of the accelerator.

Detector tracking run plan

1.) Set the TDC to clear unless there is a coincidence.

The FAST CLEAR on the CAEN 775 TDC did not work like the Fast CLEAR on the CAEN 792. Instead we decided to reset the TDC unless a coincidence pulse is generated which will veto the ADC FAST clear and the TDC reset pulses so they don't happen.

3/25/10

Detector tracking run plan

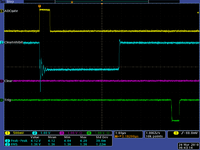

The VFAT cables delay the GEM trigout pulse by about 229 ns:

Cable delay time is 100 ft + 6 ft + 5 ft = 111 ft (30.96 cm/ft) (1 ns/15 cm) = 229nsec

The VFATs have a latency switch which goes back in time by MCLK cycles.

The MCLK is set to 40 MHz so the latency interval is

Latency = 1/MCLK = 1/40 MHz = 25 ns

229ns/25ns = 9.2 = latency value for VFAT to time in signal from the HRRL cell to the HRRL counting room

We should be able to get the VFAT measurement in time by setting the latency to 9 clock pulses.

First though, set the latency to 0 and set the VFAT threshold so you don;t see any hits.

Then, study how the hits in the VFAT change with latency by changing the latency between values of 6-12.

end the day with everything in time

3/26/10

Work on collimation to optimize detector coincidence and rate. We want a coincidence in all 5 detectors with no pileup.

This means collimation and reduced current.

Once set up we should just take data all day to practice tracking. First take a sample with coincidence on front and rear PMTs (2 hours). Then add the Rear Drift chamber (2 hours). and then finally see if the GEM trigout can be added and finish running with this configuration.