Difference between revisions of "CAEN V775 TDC"

(→Timing) |

|||

| (36 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

[[Media:Manual_CAEN_775_TDC.pdf]] | [[Media:Manual_CAEN_775_TDC.pdf]] | ||

| + | |||

| + | The 12 bit ADC conversion time is 5.7 <math>\mu</math>s. A sliding scale technique is used to reduce differential nonlinearity by injecting an offset. This reduces the dynamic range to 0 <math>\Rightarrow</math> 3840. ADC values between 3841 and 4095 indicate an error. | ||

| + | |||

| + | The TDC measures the time interval between the falling ECL inputs to the start/stop and the channel. | ||

| + | |||

| + | You can change the dynamic range of the TDC by setting bits using the library function c775setFSR. | ||

[[Image:CAEN_V775_TDCAddress.jpg | 400 px]] | [[Image:CAEN_V775_TDCAddress.jpg | 400 px]] | ||

| Line 23: | Line 29: | ||

| − | =Common Start/Stop | + | =Common Start/Stop= |

| Line 29: | Line 35: | ||

0 => common start | 0 => common start | ||

| − | |||

1 => common start | 1 => common start | ||

| Line 57: | Line 62: | ||

Use PrintEvent to print out the data in the TDC to the ROC console | Use PrintEvent to print out the data in the TDC to the ROC console | ||

| − | |||

| + | -> c775PrintEvent | ||

| + | TDC DATA for Module 0 | ||

| + | Header: 0xfa000100 nWords = 1 | ||

| + | 0xf80048b8 | ||

| + | Trailer: 0xfc00005a Event Count = 90 | ||

| + | value = 3 = 0x3 | ||

| + | |||

| + | |||

| + | ==Decoding the data== | ||

| + | |||

| + | ===Header=== | ||

| + | Header = 0xfa000100 = 11111010000000000000000100000000 b | ||

| + | |||

| + | bits 27-31 contain the GEO address = 11111 d = 0xF | ||

| + | |||

| + | bits 26-24 contain the type of word 010 => header | ||

| + | |||

| + | bits 16-23 contain the crate number = 00000000 => crate 0 | ||

| + | |||

| + | bits 8-13 contain the number of channels contained in the data word = 000001 = 1 TDC channel | ||

| + | |||

| + | === Data Words=== | ||

| + | |||

| + | data = 0xf80048b8 = 11111000000000000100100010111000 b | ||

| + | |||

| + | bits 27-31 contain the GEO address = 11111 d = 0xF | ||

| + | |||

| + | bits 26-24 contain the type of word 000 => dataum | ||

| + | |||

| + | bits 16-20 contain the channel number = 00000 => channel 0 | ||

| + | |||

| + | bit 14 = data valid bit = 1 => valid data | ||

| + | |||

| + | bit 13 = underthreshold bit | ||

| + | |||

| + | bit 12 = overflow bit 0 => ADC not in overflow | ||

| + | |||

| + | bits 0-11 contain the TDC value = 100010111000 b = 0x8b8 = 2232 d | ||

| + | |||

| + | |||

| + | The TDC value for channel 0 is 2232 channels. | ||

| + | |||

| + | The manuals says the TDC has a range from 140 ns to 1.2 \mu s with 8 bit resolution. | ||

| + | |||

| + | === The Trailer structure=== | ||

| + | Trailer: 0xfc00005a Event Count = 90 | ||

| + | |||

| + | == Measuring the TDC range== | ||

| + | |||

| + | I used the Stanford pulse generator to generate 2 NIM pulses and then sent those to a NIM to ECL converter in order to create 2 ECL pulses which the TDC accepts as input. | ||

| + | |||

| + | |||

| + | I set the delays to | ||

| + | |||

| + | A = T+0 | ||

| + | |||

| + | B = T+ 60 ns | ||

| + | |||

| + | C = T+ 70 ns | ||

| + | |||

| + | D = T + 130 ns | ||

| + | |||

| + | |||

| + | The TDC data bits were = 010000100001 b = 1057 d | ||

| + | |||

| + | |||

| + | |||

| + | Change the delays on "C" and "D" to: | ||

| + | |||

| + | |||

| + | A = T+0 | ||

| + | |||

| + | B = T+ 60 ns | ||

| + | |||

| + | C = T+ 100 ns | ||

| + | |||

| + | D = T + 150 ns | ||

| + | |||

| + | And the TDC bits become = 010111010001 b = 1489 d | ||

| + | |||

| + | |||

| + | Change the delays on "C" and "D" to: | ||

| + | |||

| + | |||

| + | A = T+0 | ||

| + | |||

| + | B = T+ 60 ns | ||

| + | |||

| + | C = T+ 150 ns | ||

| + | |||

| + | D = T + 200 ns | ||

| + | |||

| + | TDC bits = 100110010011 b = 2451 d | ||

| + | |||

| + | Change the delays on "C" and "D" to: | ||

| + | |||

| + | A = T+0 | ||

| + | |||

| + | B = T+ 60 ns | ||

| + | |||

| + | C = T+ 200 ns | ||

| + | |||

| + | D = T + 250 ns | ||

| + | |||

| + | |||

| + | The TDC can only measure time intervals up to about 250 ns. | ||

| + | |||

| + | |||

| + | |||

| + | For Channel 0 I injected the pulses | ||

| + | |||

| + | [[Image:V795_TDCtestPulses_11-28-08.png | 200 px]] | ||

| + | 10111110110 b = 1526 d | ||

| + | |||

| + | |||

| + | |||

| + | Data = 0xf80048b1 = 11111000000000000100100010110001 b | ||

| + | |||

| + | bits 0-11 = 100010110001 b = 2225 d = 0x 8b1 | ||

| + | |||

| + | [[Image:V795_TDCtestPulses_11-28-08_1400ns.png | 200 px]] | ||

| + | |||

| + | === EOB / Trailer === | ||

| + | |||

| + | |||

| + | == Full Scale Register== | ||

| + | |||

| + | Apparently the TDC default is sets the full scale register to 250 ns. The TDC can go up to 1200 ns, see pg 59 of manual of the manual. | ||

| + | |||

| + | The VME function | ||

| + | |||

| + | c775SetFSR(id, fsr) | ||

| + | |||

| + | can be used to set the Full scale register to the desired value. | ||

| + | |||

| + | |||

| + | I found the FSR value was 440 | ||

| + | |||

| + | |||

| + | -> c775SetFSR(0,0) | ||

| + | value = 440 = 0x1b8 | ||

| + | |||

| + | |||

| + | Now set it to 880 and see if TDC range doubles: | ||

| + | |||

| + | -> c775SetFSR(0,880) | ||

| + | value = 880 = 0x370 | ||

| + | -> c775SetFSR(0,0) | ||

| + | value = 880 = 0x370 | ||

| + | |||

| + | My stanford gate delay generator was set to | ||

| + | |||

| + | A = T+0 | ||

| + | |||

| + | B = T+ 60 ns | ||

| + | |||

| + | C = T+ 150 ns | ||

| + | |||

| + | D = T + 200 ns | ||

| + | |||

| + | When the FSR was set to 440 I saw | ||

| + | |||

| + | TDC bits = 100110010011 b = 2451 d | ||

| + | |||

| + | Now at 880 I see | ||

| + | |||

| + | TDC bits = 010000000101 b = 1029 d | ||

| + | |||

| + | ==Checking data word channel number == | ||

| + | |||

| + | |||

| + | 0xf802440d = 11111000000000100100010000001101 b => bit 17 is high which means channel 2 d (10 b) | ||

| + | |||

| + | <math> t ({\rm ns}) = \frac{1000 {\rm ns}}{2^{12}{\rm chan}} \times Number of {\rm chan} </math> | ||

| + | |||

| + | ==Timing== | ||

| + | |||

| + | TDC start time = fall of the negative NIM pulse.<br> | ||

| + | TDC stop time = fall of the negative NIM pulse. | ||

| − | [http:// | + | [http://wiki.iac.isu.edu/index.php/VME_modules Go back] |

| + | [[VME_modules]] Go back | ||

Latest revision as of 15:24, 16 July 2012

The 12 bit ADC conversion time is 5.7 s. A sliding scale technique is used to reduce differential nonlinearity by injecting an offset. This reduces the dynamic range to 0 3840. ADC values between 3841 and 4095 indicate an error.

The TDC measures the time interval between the falling ECL inputs to the start/stop and the channel.

You can change the dynamic range of the TDC by setting bits using the library function c775setFSR.

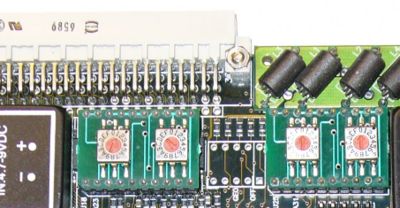

| Address | |

| Pin | Setting |

| SW 1 | 1 |

| SW 2 | 6 |

| SW 3 | 0 |

| SW 4 | 8 |

initialize TDC

-> c775Init(0x610000) Initialized TDC ID 0 at address 0x90610000

Common Start/Stop

BitSet 2 is used to set the TDC in common start or stop mode.

0 => common start 1 => common start

Use the Status function to see what the bit is set at

-> c775Status(0)

STATUS for TDC id 0 at base address 0x90610000

----------------------------------------------

Interrupts Disabled

Last Interrupt Count : 0

--1-- --2--

Status = 0x0050 0x0002

BitSet = 0x0000 0x0898

Control = 0x0000

FSR = 140 nsec

Event Count = (No Events Taken)

Last Event Read = (No Events Read)

value = 37 = 0x25 = '%'

BitSet 2 is set to 0x0898 = 100010011000 d

The above has bit 10 ( starting from 0 at the very left) set to 0 => common start

Read Data

Use PrintEvent to print out the data in the TDC to the ROC console

-> c775PrintEvent

TDC DATA for Module 0

Header: 0xfa000100 nWords = 1

0xf80048b8

Trailer: 0xfc00005a Event Count = 90

value = 3 = 0x3

Decoding the data

Header

Header = 0xfa000100 = 11111010000000000000000100000000 b

bits 27-31 contain the GEO address = 11111 d = 0xF

bits 26-24 contain the type of word 010 => header

bits 16-23 contain the crate number = 00000000 => crate 0

bits 8-13 contain the number of channels contained in the data word = 000001 = 1 TDC channel

Data Words

data = 0xf80048b8 = 11111000000000000100100010111000 b

bits 27-31 contain the GEO address = 11111 d = 0xF

bits 26-24 contain the type of word 000 => dataum

bits 16-20 contain the channel number = 00000 => channel 0

bit 14 = data valid bit = 1 => valid data

bit 13 = underthreshold bit

bit 12 = overflow bit 0 => ADC not in overflow

bits 0-11 contain the TDC value = 100010111000 b = 0x8b8 = 2232 d

The TDC value for channel 0 is 2232 channels.

The manuals says the TDC has a range from 140 ns to 1.2 \mu s with 8 bit resolution.

The Trailer structure

Trailer: 0xfc00005a Event Count = 90

Measuring the TDC range

I used the Stanford pulse generator to generate 2 NIM pulses and then sent those to a NIM to ECL converter in order to create 2 ECL pulses which the TDC accepts as input.

I set the delays to

A = T+0

B = T+ 60 ns

C = T+ 70 ns

D = T + 130 ns

The TDC data bits were = 010000100001 b = 1057 d

Change the delays on "C" and "D" to:

A = T+0

B = T+ 60 ns

C = T+ 100 ns

D = T + 150 ns

And the TDC bits become = 010111010001 b = 1489 d

Change the delays on "C" and "D" to:

A = T+0

B = T+ 60 ns

C = T+ 150 ns

D = T + 200 ns

TDC bits = 100110010011 b = 2451 d

Change the delays on "C" and "D" to:

A = T+0

B = T+ 60 ns

C = T+ 200 ns

D = T + 250 ns

The TDC can only measure time intervals up to about 250 ns.

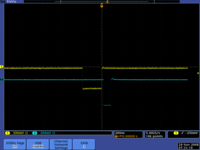

For Channel 0 I injected the pulses

Data = 0xf80048b1 = 11111000000000000100100010110001 b

bits 0-11 = 100010110001 b = 2225 d = 0x 8b1

EOB / Trailer

Full Scale Register

Apparently the TDC default is sets the full scale register to 250 ns. The TDC can go up to 1200 ns, see pg 59 of manual of the manual.

The VME function

c775SetFSR(id, fsr)

can be used to set the Full scale register to the desired value.

I found the FSR value was 440

-> c775SetFSR(0,0) value = 440 = 0x1b8

Now set it to 880 and see if TDC range doubles:

-> c775SetFSR(0,880) value = 880 = 0x370 -> c775SetFSR(0,0) value = 880 = 0x370

My stanford gate delay generator was set to

A = T+0

B = T+ 60 ns

C = T+ 150 ns

D = T + 200 ns

When the FSR was set to 440 I saw

TDC bits = 100110010011 b = 2451 d

Now at 880 I see

TDC bits = 010000000101 b = 1029 d

Checking data word channel number

0xf802440d = 11111000000000100100010000001101 b => bit 17 is high which means channel 2 d (10 b)

Timing

TDC start time = fall of the negative NIM pulse.

TDC stop time = fall of the negative NIM pulse.

Go back VME_modules Go back