Difference between revisions of "JLab F250ADC"

| (79 intermediate revisions by 2 users not shown) | |||

| Line 2: | Line 2: | ||

It has a mini trigger connector which requires another VME board to convert from the standard lemo input to this mini input. | It has a mini trigger connector which requires another VME board to convert from the standard lemo input to this mini input. | ||

| + | |||

| + | = Properties= | ||

| + | |||

| + | The 0.5 Volt setting has problems | ||

| + | |||

| + | The board I currently have is a 10 bit ADC but there is an internal shift making the value 12 bit. The lower bits are doubled up to do this. | ||

| + | |||

| + | running at 250 MHz => 4 ns | ||

| + | |||

| + | <math>\frac{1V}{2^{12} \mbox{chan}} = \frac{1V}{4096 \mbox{chan}} = 244 \frac{\mu \mbox{Volt}}{\mbox{chan}} \frac{1}{50 \Omega} 4 \times 10^{-9} s = 20 \frac{\mbox{fC}}{\mbox{chan}}</math> | ||

| + | |||

| + | CAEN V792 was <math>100 \frac{\mbox{fC}}{\mbox{counts}}</math> | ||

| + | |||

| + | |||

| + | The timing window can be as long as 4 <math>\mu</math> sec. | ||

| + | |||

| + | The trigger must occur at least a few clock cycles after the pulse in order to capture all of the pulse in the window. | ||

= Addressing= | = Addressing= | ||

| Line 80: | Line 97: | ||

|} | |} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

=Software Trigger= | =Software Trigger= | ||

==Initialize FADC for software trigger mode== | ==Initialize FADC for software trigger mode== | ||

| Line 126: | Line 104: | ||

faInit(0xbb0000,0,0,0) | faInit(0xbb0000,0,0,0) | ||

| − | -> faInit(0xbb0000,0,0,0) | + | -> faInit(0xbb0000,0,0,0) |

| − | Initialized FADC 0 Slot # | + | Initialized FADC 0 Slot # 7 at address 0x90bb0000 |

faInit: Enabling FADC Internal Clock, and Software Triggers (Soft Sync Reset) | faInit: Enabling FADC Internal Clock, and Software Triggers (Soft Sync Reset) | ||

value = 0 = 0x0 | value = 0 = 0x0 | ||

| − | ;Notice FADC ID is 0 in Slot | + | ;Notice FADC ID is 0 in Slot 7 (the slots are number according to their location from the left most slot in the crate which starts counting at 1) |

== define processing mode== | == define processing mode== | ||

| Line 142: | Line 120: | ||

unsigned int NSB, unsigned int NSA, unsigned int NP, int bank) | unsigned int NSB, unsigned int NSA, unsigned int NP, int bank) | ||

| + | |||

| + | id = slot number | ||

An example of this should be in one of the Readout lists, however, right now there are 3 viable processing modes (pmode =1,2 or 3) | An example of this should be in one of the Readout lists, however, right now there are 3 viable processing modes (pmode =1,2 or 3) | ||

| Line 150: | Line 130: | ||

pmode = 3 Integral pulse mode: NSA+NSB+1 samples are summed and the sum | pmode = 3 Integral pulse mode: NSA+NSB+1 samples are summed and the sum | ||

along with the timestmp for the threshold crossing are saved. | along with the timestmp for the threshold crossing are saved. | ||

| + | |||

| + | |||

| + | PL = latency = PL=20 => 200 nsec; time delay to record measurements after trigger is received and time window begins | ||

| + | |||

| + | PTW= 20 => 80 nsecPulse Time width = time interval window for measurements | ||

| + | |||

| + | |||

| + | Assuming the Clock is 250 MHz => clock pulse widths are 4 nsec | ||

| + | |||

</pre> | </pre> | ||

| − | faSetProcMode( | + | faSetProcMode(7,1,40,38,3,6,1,0) |

| Line 158: | Line 147: | ||

<pre> | <pre> | ||

| + | -> faStatus(0) | ||

| − | + | STATUS for FADC in slot 7 at base address 0x90bb0000 | |

| − | |||

| − | STATUS for FADC in slot | ||

-------------------------------------------------- | -------------------------------------------------- | ||

Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 | Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 | ||

| Line 179: | Line 167: | ||

Software Sync Reset ENABLED | Software Sync Reset ENABLED | ||

| − | ADC Processing Configuration: ( | + | ADC Processing Configuration: (0x0018 0x0018) |

Channel Disable Mask = 0x0000 | Channel Disable Mask = 0x0000 | ||

Resolution = 10 bits | Resolution = 10 bits | ||

| − | Mode = 1 ( | + | Mode = 1 (ENABLED) |

| − | Lookback (PL) = | + | Lookback (PL) = 160 ns Time Window (PTW) = 152 ns |

| − | Time Before Peak = | + | Time Before Peak = 12 ns Time After Peak = 24 ns |

| − | Max Peak Count = | + | Max Peak Count = 1 |

CSR Register = 0x006318e0 | CSR Register = 0x006318e0 | ||

| Line 194: | Line 182: | ||

Events in FIFO = 0 (Block level = 1) | Events in FIFO = 0 (Block level = 1) | ||

value = 44 = 0x2c = ',' | value = 44 = 0x2c = ',' | ||

| − | |||

</pre> | </pre> | ||

| Line 235: | Line 222: | ||

-> faTrig(0) | -> faTrig(0) | ||

value = -1866792960 = 0x90bb0000 = tclOpenFiles + 0x82ef31a0 | value = -1866792960 = 0x90bb0000 = tclOpenFiles + 0x82ef31a0 | ||

| + | </pre> | ||

| + | |||

| + | The output was different on 5/6/11: | ||

| + | |||

| + | <pre> | ||

| + | -> faTrig(0) | ||

| + | value = -1866792960 = 0x90bb0000 = fadc_data + 0x82ee9c00 | ||

</pre> | </pre> | ||

==check if there is an event in the FIFO== | ==check if there is an event in the FIFO== | ||

<pre> | <pre> | ||

| + | -> faStatus(0) | ||

| − | + | STATUS for FADC in slot 7 at base address 0x90bb0000 | |

| − | STATUS for FADC in slot | ||

-------------------------------------------------- | -------------------------------------------------- | ||

Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 | Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 | ||

| Line 259: | Line 253: | ||

Software Sync Reset ENABLED | Software Sync Reset ENABLED | ||

| − | ADC Processing Configuration: ( | + | ADC Processing Configuration: (0x0018 0x0018) |

Channel Disable Mask = 0x0000 | Channel Disable Mask = 0x0000 | ||

Resolution = 10 bits | Resolution = 10 bits | ||

| − | Mode = 1 ( | + | Mode = 1 (ENABLED) |

| − | Lookback (PL) = | + | Lookback (PL) = 160 ns Time Window (PTW) = 152 ns |

| − | Time Before Peak = | + | Time Before Peak = 12 ns Time After Peak = 24 ns |

| − | Max Peak Count = | + | Max Peak Count = 1 |

| − | CSR Register = | + | CSR Register = 0x006318e7 |

Control 1 Register = 0x00030eef | Control 1 Register = 0x00030eef | ||

Control 2 Register = 0x00000007 - Enabled for triggers | Control 2 Register = 0x00000007 - Enabled for triggers | ||

Internal Triggers (Live) = 0 | Internal Triggers (Live) = 0 | ||

Trigger Scaler = 1 | Trigger Scaler = 1 | ||

| − | + | Blocks in FIFO = 1 (Block level = 1) - Block Available | |

RAM Level (Bytes) = 0 | RAM Level (Bytes) = 0 | ||

value = 26 = 0x1a | value = 26 = 0x1a | ||

| − | + | ||

</pre> | </pre> | ||

| Line 295: | Line 289: | ||

FPGA2: wc=0 Empty=1 Full=0 | FPGA2: wc=0 Empty=1 Full=0 | ||

value = 34 = 0x22 = '"' | value = 34 = 0x22 = '"' | ||

| + | </pre> | ||

| + | |||

| + | The output on 5/6/11 was: | ||

| + | |||

| + | <pre> | ||

| + | Fifo Buffers Status (DataFlow Status = 0x0003810d | ||

| + | Input Buffer : 0x90009000 | ||

| + | FPGA1: wc=0 Empty=1 Full=0 Ready=1 | ||

| + | FPGA2: wc=0 Empty=1 Full=0 Ready=1 | ||

| + | Build Buffer : 0x10001000 | ||

| + | FPGA1: wc=0 Empty=1 Full=0 | ||

| + | FPGA2: wc=0 Empty=1 Full=0 | ||

| + | Output Buffer: 0x00900090 | ||

| + | FPGA1: wc=144 Empty=0 Full=0 | ||

| + | FPGA2: wc=144 Empty=0 Full=0 | ||

| + | value = 36 = 0x24 = '$' | ||

</pre> | </pre> | ||

| Line 307: | Line 317: | ||

==try to read a block== | ==try to read a block== | ||

| + | |||

| + | I stil don't see channel 1 or 3 in the output? | ||

<pre> | <pre> | ||

| Line 585: | Line 597: | ||

=Hardware Trigger= | =Hardware Trigger= | ||

| + | ==Install DMA lib== | ||

| + | |||

| + | ===Configure ROC === | ||

| + | ====Load the library==== | ||

| + | <pre> | ||

| + | |||

| + | -> ld < usrTempeDma.o | ||

| + | value = 230900496 = 0xdc34310 | ||

| + | </pre> | ||

| + | |||

| + | ====Configure the Memory ==== | ||

| + | |||

| + | <pre> | ||

| + | -> usrVmeDmaConfig(2,2,0) | ||

| + | 0xdbb1830 (tShell): VME DMA Address Mode set for A32 | ||

| + | 0xdbb1830 (tShell): VME DMA Transfer Mode set for D32 block mode (BLT) | ||

| + | value = 0 = 0x0 | ||

| + | </pre> | ||

| + | ====Show the Dma config==== | ||

| + | <pre> | ||

| + | -> sysVmeDmaShow | ||

| + | DMA Chan 0 Status = 0x00290000 | ||

| + | Source(VME) address: 0x002b0000 | ||

| + | Destination address: 0x0020efb4 | ||

| + | Byte Count : 0x00007356 | ||

| + | Execption Status : 0x00000000 | ||

| + | Bus Error address: 0x00000000 | ||

| + | DMA Control Reg : 0x00000000 | ||

| + | VME Address Mode : 2 (A32) | ||

| + | VME Data Width : 1 (D32) | ||

| + | VME Transfer Mode: 1 (BLT32) | ||

| + | STATUS of Last Transfer: | ||

| + | NO Transfer Completed | ||

| + | value = 2686976 = 0x290000 | ||

| + | -> ld < fadcLib.o | ||

| + | value = 230935520 = 0xdc3cbe0 | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | ;Click Prestart | ||

| + | |||

| + | <pre> | ||

| + | daLogMsg: INFO: Entering User Prestart | ||

| + | linking async GEN trigger to id 1 | ||

| + | |||

| + | disconnecting vector 225 | ||

| + | |||

| + | STATUS for FADC in slot 7 at base address 0x90bb0000 | ||

| + | -------------------------------------------------- | ||

| + | Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 | ||

| + | Alternate VME Addressing: Multiblock Disabled | ||

| + | A32 Enabled at VME base 0x08000000 or CPU addr 0x80000000 | ||

| + | Signal Sources: | ||

| + | Ref Clock : Front Panel | ||

| + | Trig Src : Front Panel (Async) | ||

| + | Sync Reset: Front Panel (Async) | ||

| + | SDC : In Use | ||

| + | |||

| + | Configuration: | ||

| + | Internal Clock ON | ||

| + | Bus Error ENABLED | ||

| + | MultiBlock transfer DISABLED | ||

| + | |||

| + | ADC Processing Configuration: (0x0018 0x0018) | ||

| + | Channel Disable Mask = 0x0000 | ||

| + | Resolution = 10 bits | ||

| + | Mode = 1 (ENABLED) | ||

| + | Lookback (PL) = 200 ns Time Window (PTW) = 80 ns | ||

| + | Time Before Peak = 12 ns Time After Peak = 24 ns | ||

| + | Max Peak Count = 1 | ||

| + | |||

| + | CSR Register = 0x006318e0 | ||

| + | Control 1 Register = 0x00130119 | ||

| + | Control 2 Register = 0x0000000f - Enabled for triggers | ||

| + | Internal Triggers (Live) = 0 | ||

| + | Trigger Scaler = 0 | ||

| + | Events in FIFO = 0 (Block level = 1) | ||

| + | </pre> | ||

| + | |||

| + | ; Click Go | ||

| + | |||

| + | <pre> | ||

| + | daLogMsg: INFO: Entering User Go | ||

| + | 0xdca6890 (ROC): faSync: ERROR: Software Sync Resets not enabledinterrupt: ERROR: NO data in FADC datascan = 0x0 | ||

| + | |||

| + | </pre> | ||

| + | now trigger one time | ||

| + | |||

| + | <pre> | ||

| + | -> faStatus(0) | ||

| + | |||

| + | STATUS for FADC in slot 7 at base address 0x90bb0000 | ||

| + | -------------------------------------------------- | ||

| + | Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 | ||

| + | Alternate VME Addressing: Multiblock Disabled | ||

| + | A32 Enabled at VME base 0x08000000 or CPU addr 0x80000000 | ||

| + | |||

| + | Signal Sources: | ||

| + | Ref Clock : Front Panel | ||

| + | Trig Src : Front Panel (Async) | ||

| + | Sync Reset: Front Panel (Async) | ||

| + | SDC : In Use | ||

| + | |||

| + | Configuration: | ||

| + | Internal Clock ON | ||

| + | Bus Error ENABLED | ||

| + | MultiBlock transfer DISABLED | ||

| + | |||

| + | ADC Processing Configuration: (0x0018 0x0018) | ||

| + | Channel Disable Mask = 0x0000 | ||

| + | Resolution = 10 bits | ||

| + | Mode = 1 (ENABLED) | ||

| + | Lookback (PL) = 200 ns Time Window (PTW) = 80 ns | ||

| + | Time Before Peak = 12 ns Time After Peak = 24 ns | ||

| + | Max Peak Count = 1 | ||

| + | |||

| + | CSR Register = 0x006318e8 | ||

| + | Control 1 Register = 0x00130119 | ||

| + | Control 2 Register = 0x0000000f - Enabled for triggers | ||

| + | Internal Triggers (Live) = 0 | ||

| + | Trigger Scaler = 1 | ||

| + | Events in FIFO = 0 (Block level = 1) | ||

| + | value = 44 = 0x2c = ',' | ||

| + | -> sysVmeDmaShow | ||

| + | DMA Chan 0 Status = 0x10000000 | ||

| + | Source(VME) address: 0x08000800 | ||

| + | Destination address: 0x0d152e30 | ||

| + | Byte Count : 0x00003680 | ||

| + | Execption Status : 0x000ccb00 | ||

| + | Bus Error address: 0x080002b8 | ||

| + | DMA Control Reg : 0x00836070 | ||

| + | VME Address Mode : 2 (A32) | ||

| + | VME Data Width : 1 (D32) | ||

| + | VME Transfer Mode: 1 (BLT32) | ||

| + | STATUS of Last Transfer: | ||

| + | Error Bit Set | ||

| + | Source: VME Bus | ||

| + | value = 268435456 = 0x10000000 | ||

| + | </pre> | ||

| + | |||

| + | There is an error bit set. | ||

| + | |||

| + | ;Second Trigger | ||

| + | |||

| + | no change | ||

| + | |||

| + | ; Third Trigger | ||

| + | |||

| + | <pre> | ||

| + | -> interrupt: ERROR: Data still in FADC (event 4, scan 0x1 csr 0xf06318ef ) - clearing | ||

| + | </pre> | ||

| + | |||

| + | |||

| + | ROC crashes | ||

==Setup Signal distribution board== | ==Setup Signal distribution board== | ||

| − | === | + | ===FADC and SD address=== |

The ADC address pins are set to | The ADC address pins are set to | ||

| Line 657: | Line 823: | ||

0xea = 1110101000 | 0xea = 1110101000 | ||

| + | ==Initialize FADC for Front panel(FP) trigger with Signal distribution (SD) board== | ||

| − | + | The address of the SD board is passed to the faInit routine | |

| + | |||

| + | Using the SD boards's internal clock | ||

| + | <pre> | ||

| + | -> faInit(0xbb0000,0,0,0xea13) | ||

| + | Initialized FADC 0 Slot # 7 at address 0x90bb0000 | ||

| + | Using JLAB FADC Signal Distribution Module at address 0x9100ea00 | ||

| + | faInit: JLAB FADC Signal Distribution Card is Assumed in Use | ||

| + | faInit: Front Panel Inputs will be enabled. | ||

| + | faInit: Enabling FADC for SDC Clock (Front Panel) and Front Panel Triggers (FP Sync Reset) | ||

| + | value = 0 = 0x0 | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | |||

| + | or using the FADC's internal clock | ||

| − | -> faInit( | + | <pre> |

| − | faInit: | + | -> faInit(0xbb0000,0,0,0xea03) |

| + | Initialized FADC 0 Slot # 7 at address 0x90bb0000 | ||

| + | Using JLAB FADC Signal Distribution Module at address 0x9100ea00 | ||

| + | faInit: JLAB FADC Signal Distribution Card will not be Used | ||

faInit: Enabling FADC Internal Clock, and Front Panel Triggers (FP Sync Reset) | faInit: Enabling FADC Internal Clock, and Front Panel Triggers (FP Sync Reset) | ||

| − | + | value = 0 = 0x0 | |

| − | value = | + | </pre> |

| + | |||

| + | ==faSDC_Status== | ||

| + | |||

| + | <pre> | ||

| + | -> faSDC_Status(0) | ||

| + | |||

| + | STATUS for FADC Signal Distribution Card at base address 0x9100ea00 | ||

| + | ---------------------------------------------------------------- | ||

| + | Board Firmware Rev/ID = 0x02 | ||

| + | Registers: | ||

| + | CSR = 0x0200 Control = 0x0220 | ||

| + | Busy Enable = 0x0000 Busy Status = 0xfe00 | ||

| + | |||

| + | Ref Clock : Internal | ||

| + | Software Triggers | ||

| + | Software Sync Reset | ||

| + | value = 21 = 0x15 | ||

| + | </pre> | ||

| + | The SDC has not been eneabled yet for external triggers. | ||

| − | + | Use faGEnable(0,0) to enable both the FADC and the SD board | |

| − | + | -> faGEnable(0,0) | |

| + | value = 1 = 0x1 | ||

| + | -> faSDC_Status(0) | ||

| − | - | + | STATUS for FADC Signal Distribution Card at base address 0x9100ea00 |

| − | + | ---------------------------------------------------------------- | |

| − | + | Board Firmware Rev/ID = 0x02 | |

| + | Registers: | ||

| + | CSR = 0x0200 Control = 0x0200 | ||

| + | Busy Enable = 0x0000 Busy Status = 0xfe00 | ||

| + | |||

| + | Ref Clock : Internal | ||

| + | External Triggers (Sync with clock) | ||

| + | Software Sync Reset | ||

| + | value = 21 = 0x15 | ||

| + | |||

| + | == Set the FADC processing mode== | ||

| + | -> faSetProcMode(7,1,40,38,3,6,1,0) | ||

value = 0 = 0x0 | value = 0 = 0x0 | ||

| + | <pre> | ||

| + | int | ||

| + | faSetProcMode(int id, int pmode, unsigned int PL, unsigned int PTW, | ||

| + | unsigned int NSB, unsigned int NSA, unsigned int NP, int bank) | ||

| + | |||

| + | |||

| + | id = slot number =7 | ||

| + | |||

| + | An example of this should be in one of the Readout lists, however, right now there are 3 viable processing modes (pmode =1,2 or 3) | ||

| + | |||

| + | pmode = 1 RAW Window mode: all samples within PTW are saved | ||

| + | pmode = 2 RAW Pulse mode: NSA+NSB+1 samples around a threshold crossing | ||

| + | are saved. | ||

| + | pmode = 3 Integral pulse mode: NSA+NSB+1 samples are summed and the sum | ||

| + | along with the timestmp for the threshold crossing are saved. | ||

| + | |||

| + | |||

| + | PL = 40 = 160 ns = programmable latency ; time delay to record measurements after trigger is received and time window begins | ||

| + | |||

| + | PTW= 20 => 80 nsecPulse Time width = time interval window for measurements | ||

| + | = number of samples in the pulse time window moving forward in time from the location of the latency. | ||

| + | |||

| + | |||

| + | |||

| + | NSB = 3 = Number of Samples before before the pulse to record | ||

| + | |||

| + | NSA=6 = number of samples after the pulse to record | ||

| + | NP =1 = number of pulses to look for in the PTW | ||

| − | + | Assuming the Clock is 250 MHz => clock pulse widths are 4 nsec | |

| − | + | </pre> | |

| − | + | ==Configure SD card== | |

| + | |||

| + | <pre> | ||

/*************************************************************************************** | /*************************************************************************************** | ||

| Line 693: | Line 940: | ||

bMask: mask of Busy enables for the SDC - Do not Enable busy if there is no FADC | bMask: mask of Busy enables for the SDC - Do not Enable busy if there is no FADC | ||

| − | + | ||

| + | |||

*/ | */ | ||

int | int | ||

faSDC_Config(unsigned short cFlag, unsigned short bMask) | faSDC_Config(unsigned short cFlag, unsigned short bMask) | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | -> faSDC_Config(0,0) | ||

| + | value = 0 = 0x0 | ||

| + | |||

| + | ==FADC status== | ||

| + | |||

| + | <pre> | ||

| + | -> faStatus(0) | ||

| + | |||

| + | STATUS for FADC in slot 7 at base address 0x90bb0000 | ||

| + | -------------------------------------------------- | ||

| + | Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 | ||

| + | Alternate VME Addressing: Multiblock Disabled | ||

| + | A32 Enabled at VME base 0x08000000 or CPU addr 0x80000000 | ||

| + | |||

| + | Signal Sources: | ||

| + | Ref Clock : Front Panel | ||

| + | Trig Src : Front Panel (Async) | ||

| + | Sync Reset: Front Panel (Async) | ||

| + | SDC : In Use | ||

| + | |||

| + | Configuration: | ||

| + | Internal Clock ON | ||

| + | Bus Error DISABLED | ||

| + | MultiBlock transfer DISABLED | ||

| + | |||

| + | ADC Processing Configuration: (0x0018 0x0018) | ||

| + | Channel Disable Mask = 0x0000 | ||

| + | Resolution = 10 bits | ||

| + | Mode = 1 (ENABLED) | ||

| + | Lookback (PL) = 160 ns Time Window (PTW) = 152 ns | ||

| + | Time Before Peak = 12 ns Time After Peak = 24 ns | ||

| + | Max Peak Count = 1 | ||

| + | |||

| + | CSR Register = 0x00631ce0 | ||

| + | Control 1 Register = 0x00030119 | ||

| + | Control 2 Register = 0x00000007 - Enabled for triggers | ||

| + | Internal Triggers (Live) = 0 | ||

| + | Trigger Scaler = 0 | ||

| + | Events in FIFO = 0 (Block level = 1) | ||

| + | value = 44 = 0x2c = ',' | ||

| + | </pre> | ||

| + | |||

| + | = Test pulse Measurment= | ||

| + | |||

| + | Input the test pulse below into the FADC | ||

| + | |||

| + | [[File:FADCTestPulse_05182011.png|200 px]] | ||

| + | |||

| + | I set a delay for 200 ns and a pulse window for 40 ns. | ||

| + | |||

| + | <pre> | ||

| + | |||

| + | faSetProcMode(7,1,50,10,0,0,0,0); | ||

| + | |||

| + | ADC Processing Configuration: (0xfe08 0xff08) | ||

| + | Channel Disable Mask = 0xfffe | ||

| + | Resolution = 10 bits | ||

| + | Mode = 1 (ENABLED) | ||

| + | Lookback (PL) = 200 ns Time Window (PTW) = 40 ns | ||

| + | Time Before Peak = 20 ns Time After Peak = 40 ns | ||

| + | Max Peak Count = 0 | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | RUn 2144 with 64 events | ||

| + | |||

| + | Run 2145 with | ||

| + | |||

| + | = faChanDisable= | ||

| + | |||

| + | One can disable ADC channels using the function | ||

| + | |||

| + | faChanDisable(ID,mask) | ||

| + | |||

| + | where mask is a word representing which channels you should disable with the high bit. | ||

| + | |||

| + | all 16 channels are disables with 0xffff | ||

| + | |||

| + | only channel 0 is enabled with | ||

| + | |||

| + | faChanDidable(0,0xfffe) | ||

=Documentation= | =Documentation= | ||

==Data Format== | ==Data Format== | ||

| + | |||

| + | header bank ID is =38797568=0x2500100 | ||

[[File:JLab_F250_ADC_V1.2_DataFormat.pdf]] | [[File:JLab_F250_ADC_V1.2_DataFormat.pdf]] | ||

| + | |||

| + | ==Decoding an Event== | ||

| + | |||

| + | <pre> | ||

| + | 0x00000000 0xf800fafa 0x81c00801 0x90000007 0x00000007 | ||

| + | 0x980000be 0x0001f922 0x000000be 0x0001f922 0xa0000014 | ||

| + | 0x11001100 0x11001100 0x11001100 0x11001100 0x11001100 | ||

| + | 0x11001100 0x11001100 0x11001100 0x11001100 0x11001100 | ||

| + | 0xa1000014 0x00080008 0x00040008 0x000c0008 0x00080008 | ||

| + | 0x00040008 0x00080008 0x00040004 0x00040004 0x00080004 | ||

| + | 0x00040004 0xa1800014 0x10000004 0x10000000 0x10001000 | ||

| + | 0x10001000 0x10001000 0x10001000 0x10000000 0x00000000 | ||

| + | 0x10001000 0x00001000 0xa2000014 0x00cc00cc 0x00cc00d0 | ||

| + | 0x00cc00cc 0x00cc00cc 0x00cc00d0 0x00cc00cc 0x00cc00cc | ||

| + | 0x00cc00cc 0x00cc00d0 0x00cc00cc 0xa2800014 0x00080008 | ||

| + | 0x00040008 0x00040004 0x00080004 0x00080008 0x00080008 | ||

| + | 0x00040004 0x00040008 0x00040008 0x00040008 0xa3000014 | ||

| + | 0x00140014 0x00140010 0x00140014 0x00140010 0x00100014 | ||

| + | 0x00140014 0x00140014 0x00140014 0x00140014 0x00180018 | ||

| + | 0xa3800014 0x0028002c 0x0028002c 0x002c0028 0x002c002c 0 | ||

| + | x002c002c 0x002c002c 0x002c002c 0x002c002c 0x0028002c | ||

| + | 0x002c002c 0xa4000014 0x00cc00cc 0x00cc00c8 0x00cc00cc | ||

| + | 0x00c800cc 0x00cc00cc 0x00d000cc 0x00cc00c8 0x00cc00cc | ||

| + | 0x00cc00cc 0x00cc00cc 0xa4800014 0x00cc00cc 0x00cc00cc | ||

| + | 0x00c800c8 0x00cc00cc 0x00cc00cc 0x00cc00cc 0x00cc00cc | ||

| + | 0x00cc00cc 0x00c800cc 0x00cc00c8 0xa5000014 0x00e400e4 | ||

| + | 0x00e400e4 0x00e400e4 0x00e400e8 0x00e400e4 0x00e800e4 | ||

| + | 0x00e400e4 0x00e000e4 0x00e400e4 0x00e400e4 0xa5800014 | ||

| + | 0x00c800cc 0x00c800cc 0x00cc00c8 0x00c800cc 0x00cc00c8 | ||

| + | 0x00c800cc 0x00c800cc 0x00c800cc 0x00c800c8 0x00cc00cc | ||

| + | 0xa6000014 0x00b000b0 0x00ac00b0 0x00b000b0 0x00ac00ac | ||

| + | 0x00b000b0 0x00ac00ac 0x00ac00ac 0x00b000b0 0x00b000ac | ||

| + | 0x00b000b0 0xa6800014 0x00ac00b0 0x00b000ac 0x00ac00ac | ||

| + | 0x00b000b0 0x00b000b0 0x00b000ac 0x00ac00ac 0x00b000ac | ||

| + | 0x00b000b0 0x00ac00ac 0xa7000014 0x00b800b8 0x00b400b4 | ||

| + | 0x00b400bc 0x00bc00bc 0x00b800b8 0x00b400b8 0x00b800b8 | ||

| + | 0x00b800b8 0x00b800b8 0x00b800b8 0xa7800014 0x00a000a0 | ||

| + | 0x00a400a0 0x00a000a0 0x00a000a4 0x00a400a4 0x00a400a4 | ||

| + | 0x00a000a0 0x00a000a0 0x00a000a0 0x00a400a0 0xf800ffff | ||

| + | 0x89c000ae | ||

| + | </pre> | ||

=Readoutlist example= | =Readoutlist example= | ||

| Line 931: | Line 1,309: | ||

fadcLib.h: [[Media:JLab_F250_ADC_fadcLib.h.txt]] | fadcLib.h: [[Media:JLab_F250_ADC_fadcLib.h.txt]] | ||

| + | =Errors= | ||

| + | |||

| + | ==DMA transfer error== | ||

| + | |||

| + | Click prestart in CODA to setup the FADC | ||

| + | |||

| + | then enable it for trigger | ||

| + | |||

| + | |||

| + | <pre> | ||

| + | -> faGEnable(0) | ||

| + | value = 1 = 0x1 | ||

| + | -> faStatus | ||

| + | |||

| + | STATUS for FADC in slot 7 at base address 0x90bb0000 | ||

| + | -------------------------------------------------- | ||

| + | Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 | ||

| + | Alternate VME Addressing: Multiblock Disabled | ||

| + | A32 Enabled at VME base 0x08000000 or CPU addr 0x80000000 | ||

| + | |||

| + | Signal Sources: | ||

| + | Ref Clock : Front Panel | ||

| + | Trig Src : Front Panel (Async) | ||

| + | Sync Reset: Front Panel (Async) | ||

| + | SDC : In Use | ||

| + | |||

| + | Configuration: | ||

| + | Internal Clock ON | ||

| + | Bus Error ENABLED | ||

| + | MultiBlock transfer DISABLED | ||

| + | |||

| + | ADC Processing Configuration: (0x0018 0x0018) | ||

| + | Channel Disable Mask = 0x0000 | ||

| + | Resolution = 10 bits | ||

| + | Mode = 1 (ENABLED) | ||

| + | Lookback (PL) = 200 ns Time Window (PTW) = 80 ns | ||

| + | Time Before Peak = 12 ns Time After Peak = 24 ns | ||

| + | Max Peak Count = 1 | ||

| + | |||

| + | CSR Register = 0x006318e3 | ||

| + | Control 1 Register = 0x00130119 | ||

| + | Control 2 Register = 0x00000007 - Enabled for triggers | ||

| + | Internal Triggers (Live) = 0 | ||

| + | Trigger Scaler = 2 | ||

| + | Events in FIFO = 1 (Block level = 1) - Data Available | ||

| + | RAM Level (Bytes) = 0 | ||

| + | value = 26 = 0x1a | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | |||

| + | The FIFO had events so I cleared them | ||

| + | |||

| + | <pre> | ||

| + | -> faClear | ||

| + | value = 0 = 0x0 | ||

| + | -> faStatus | ||

| + | |||

| + | STATUS for FADC in slot 7 at base address 0x90bb0000 | ||

| + | -------------------------------------------------- | ||

| + | Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 | ||

| + | Alternate VME Addressing: Multiblock Disabled | ||

| + | A32 Enabled at VME base 0x08000000 or CPU addr 0x80000000 | ||

| + | |||

| + | Signal Sources: | ||

| + | Ref Clock : Front Panel | ||

| + | Trig Src : Front Panel (Async) | ||

| + | Sync Reset: Front Panel (Async) | ||

| + | SDC : In Use | ||

| + | |||

| + | Configuration: | ||

| + | Internal Clock ON | ||

| + | Bus Error ENABLED | ||

| + | MultiBlock transfer DISABLED | ||

| + | |||

| + | ADC Processing Configuration: (0x0018 0x0018) | ||

| + | Channel Disable Mask = 0x0000 | ||

| + | Resolution = 10 bits | ||

| + | Mode = 1 (ENABLED) | ||

| + | Lookback (PL) = 200 ns Time Window (PTW) = 80 ns | ||

| + | Time Before Peak = 12 ns Time After Peak = 24 ns | ||

| + | Max Peak Count = 1 | ||

| + | |||

| + | CSR Register = 0x006318e0 | ||

| + | Control 1 Register = 0x00130119 | ||

| + | Control 2 Register = 0x00000007 - Enabled for triggers | ||

| + | Internal Triggers (Live) = 0 | ||

| + | Trigger Scaler = 0 | ||

| + | Events in FIFO = 0 (Block level = 1) | ||

| + | value = 44 = 0x2c = ',' | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | |||

| + | I did not see any random triggers so I generated one. | ||

| + | |||

| + | <pre> | ||

| + | -> faStatus | ||

| + | |||

| + | STATUS for FADC in slot 7 at base address 0x90bb0000 | ||

| + | -------------------------------------------------- | ||

| + | Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 | ||

| + | Alternate VME Addressing: Multiblock Disabled | ||

| + | A32 Enabled at VME base 0x08000000 or CPU addr 0x80000000 | ||

| + | |||

| + | Signal Sources: | ||

| + | Ref Clock : Front Panel | ||

| + | Trig Src : Front Panel (Async) | ||

| + | Sync Reset: Front Panel (Async) | ||

| + | SDC : In Use | ||

| + | |||

| + | Configuration: | ||

| + | Internal Clock ON | ||

| + | Bus Error ENABLED | ||

| + | MultiBlock transfer DISABLED | ||

| + | |||

| + | ADC Processing Configuration: (0x0018 0x0018) | ||

| + | Channel Disable Mask = 0x0000 | ||

| + | Resolution = 10 bits | ||

| + | Mode = 1 (ENABLED) | ||

| + | Lookback (PL) = 200 ns Time Window (PTW) = 80 ns | ||

| + | Time Before Peak = 12 ns Time After Peak = 24 ns | ||

| + | Max Peak Count = 1 | ||

| + | |||

| + | CSR Register = 0x006318e3 | ||

| + | Control 1 Register = 0x00130119 | ||

| + | Control 2 Register = 0x00000007 - Enabled for triggers | ||

| + | Internal Triggers (Live) = 0 | ||

| + | Trigger Scaler = 1 | ||

| + | Events in FIFO = 1 (Block level = 1) - Data Available | ||

| + | RAM Level (Bytes) = 0 | ||

| + | value = 26 = 0x1a | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | |||

| + | Let me try to print out the block | ||

| + | |||

| + | <pre> | ||

| + | -> faPrintBlock | ||

| + | 81C00801 - BLOCK HEADER - slot = 7 n_evts = 1 n_blk = 1 | ||

| + | 86C706F6 - BLOCK HEADER - slot = 27 n_evts = 224 n_blk = 1782 | ||

| + | F0000012 - DATA NOT VALID = 14 | ||

| + | value = 3 = 0x3 | ||

| + | </pre> | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | <pre> | ||

| + | -> faStatus | ||

| + | |||

| + | STATUS for FADC in slot 7 at base address 0x90bb0000 | ||

| + | -------------------------------------------------- | ||

| + | Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 | ||

| + | Alternate VME Addressing: Multiblock Disabled | ||

| + | A32 Enabled at VME base 0x08000000 or CPU addr 0x80000000 | ||

| + | |||

| + | Signal Sources: | ||

| + | Ref Clock : Front Panel | ||

| + | Trig Src : Front Panel (Async) | ||

| + | Sync Reset: Front Panel (Async) | ||

| + | SDC : In Use | ||

| + | |||

| + | Configuration: | ||

| + | Internal Clock ON | ||

| + | Bus Error ENABLED | ||

| + | MultiBlock transfer DISABLED | ||

| + | |||

| + | ADC Processing Configuration: (0x0018 0x0018) | ||

| + | Channel Disable Mask = 0x0000 | ||

| + | Resolution = 10 bits | ||

| + | Mode = 1 (ENABLED) | ||

| + | Lookback (PL) = 200 ns Time Window (PTW) = 80 ns | ||

| + | Time Before Peak = 12 ns Time After Peak = 24 ns | ||

| + | Max Peak Count = 1 | ||

| + | |||

| + | CSR Register = 0x006318e0 | ||

| + | Control 1 Register = 0x00130119 | ||

| + | Control 2 Register = 0x00000007 - Enabled for triggers | ||

| + | Internal Triggers (Live) = 0 | ||

| + | Trigger Scaler = 1 | ||

| + | Events in FIFO = 0 (Block level = 1) | ||

| + | value = 44 = 0x2c = ',' | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | clearing the module and downloading everything again seemed to make the problem go away. Also power cycling the VME crate as well. | ||

| + | |||

| + | |||

| + | :It also seems to help if you do software triggers. | ||

| + | |||

| + | ==more DMA error== | ||

| + | |||

| + | I am having trouble getting some configurations working without a DMA error. | ||

| + | |||

| + | for example | ||

| + | |||

| + | :The smallest process configuration always has a DMA error | ||

| + | |||

| + | faSetProcMode(7,1,2,1,0,0,0,0) | ||

| + | |||

| + | |||

| + | The smallest one I was able to get working without a DMA error was | ||

| + | |||

| + | faSetProcMode(7,1,20,8,0,0,0,0) | ||

| + | |||

| + | I do see the error | ||

| + | |||

| + | interrupt: ERROR: Data still in FADC (event 1039, scan 0x1 csr 0xf06318ef ) - clearing | ||

| + | |||

| + | about every 1000 +/- 500 events. | ||

| + | |||

| + | See runs 2141 and 2142 | ||

| + | |||

| + | Now I increase the latency to 200 (800 ns). | ||

| + | |||

| + | Long run 2143 was taken. | ||

| + | |||

| + | ==Extra words== | ||

| + | |||

| + | Extra data words are appearing in the FADC bank written to the CODA data file. | ||

| + | |||

| + | =Configure ADC for NaI readout= | ||

| + | |||

| + | |||

| + | The NaI detector signal width can be as much a 4 micro seconds. | ||

| + | |||

| + | That is a lot of samples | ||

| + | |||

| + | The JLab PMT output has a signal width of about 1 microsecond | ||

| + | |||

| + | Let configure the FADC to take raw samples for 2 microseconds. | ||

| + | |||

| + | You will need a latency time to determine where the window should begin since a discriminator is used to generate the ADC gate based on the NAI output. This means the ADC trigger is some time after the pulse. THis is OK because the FADC is always sampling the input in a using a time window you define. | ||

| + | |||

| + | Lets define a time window which is 2 microseconds long. | ||

| + | |||

| + | Since the clock is 250 MHz, this means each time bin is 4 ns. A timing window with 500, 4 ns bins will sum to 2 microseconds. | ||

| + | == Set timing window== | ||

| + | |||

| + | <pre> | ||

| + | int | ||

| + | faSetProcMode(int id, int pmode, unsigned int PL, unsigned int PTW, | ||

| + | unsigned int NSB, unsigned int NSA, unsigned int NP, int bank) | ||

| + | |||

| + | |||

| + | id = slot number =7 | ||

| + | |||

| + | An example of this should be in one of the Readout lists, however, right now there are 3 viable processing modes (pmode =1,2 or 3) | ||

| + | |||

| + | pmode = 1 RAW Window mode: all samples within PTW are saved | ||

| + | pmode = 2 RAW Pulse mode: NSA+NSB+1 samples around a threshold crossing | ||

| + | are saved. | ||

| + | pmode = 3 Integral pulse mode: NSA+NSB+1 samples are summed and the sum | ||

| + | along with the timestmp for the threshold crossing are saved. | ||

| + | |||

| + | |||

| + | PL = 40 = 160 ns = programmable latency ; time delay to record measurements after trigger is received and time window begins | ||

| + | |||

| + | PTW= 20 => 80 nsecPulse Time width = time interval window for measurements | ||

| + | = number of samples in the pulse time window moving forward in time from the location of the latency. | ||

| + | |||

| + | |||

| + | |||

| + | NSB = 3 = Number of Samples before before the pulse to record | ||

| + | |||

| + | NSA=6 = number of samples after the pulse to record | ||

| + | |||

| + | NP =1 = number of pulses to look for in the PTW | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | |||

| + | faSetProcMode(7,1,540,500,0,0,0,0) | ||

[[VME_modules]] | [[VME_modules]] | ||

Latest revision as of 21:14, 29 July 2011

JLab has built their own Flash ADC (called the F250)

It has a mini trigger connector which requires another VME board to convert from the standard lemo input to this mini input.

Properties

The 0.5 Volt setting has problems

The board I currently have is a 10 bit ADC but there is an internal shift making the value 12 bit. The lower bits are doubled up to do this.

running at 250 MHz => 4 ns

CAEN V792 was

The timing window can be as long as 4 sec.

The trigger must occur at least a few clock cycles after the pulse in order to capture all of the pulse in the window.

Addressing

JLab's F250 flash ADC will be used to measure the NaI output

ADdress is

| Address | ||

| Pin | Switch | bit |

| A12 | on/closed | 0 |

| A13 | on | 0 |

| A14 | on | 0 |

| A15 | on | 0 |

| A16 | on | 0 |

| A17 | off/open | 1 |

| A18 | off | 1 |

| A19 | off | 1 |

| A20 | on | 0 |

| A21 | off | 1 |

| A22 | off | 1 |

| A23 | off | 1 |

Module address = 0xee0000 = 111011100000000000000000 d

If I want 0xaa0000 = 101010100000000000000000 d

If I want 0xbb = 10111011

| Address | ||

| Pin | Switch | bit |

| A12 | on/closed | 0 |

| A13 | on | 0 |

| A14 | on | 0 |

| A15 | on | 0 |

| A16 | off | 1 |

| A17 | off/open | 1 |

| A18 | on | 0 |

| A19 | off | 1 |

| A20 | off | 1 |

| A21 | off | 1 |

| A22 | on | 0 |

| A23 | off | 1 |

Software Trigger

Initialize FADC for software trigger mode

Initialize the FADC so it will accept software triggers.

faInit(0xbb0000,0,0,0)

-> faInit(0xbb0000,0,0,0) Initialized FADC 0 Slot # 7 at address 0x90bb0000 faInit: Enabling FADC Internal Clock, and Software Triggers (Soft Sync Reset) value = 0 = 0x0

- Notice FADC ID is 0 in Slot 7 (the slots are number according to their location from the left most slot in the crate which starts counting at 1)

define processing mode

int

faSetProcMode(int id, int pmode, unsigned int PL, unsigned int PTW,

unsigned int NSB, unsigned int NSA, unsigned int NP, int bank)

id = slot number

An example of this should be in one of the Readout lists, however, right now there are 3 viable processing modes (pmode =1,2 or 3)

pmode = 1 RAW Window mode: all samples within PTW are saved

pmode = 2 RAW Pulse mode: NSA+NSB+1 samples around a threshold crossing

are saved.

pmode = 3 Integral pulse mode: NSA+NSB+1 samples are summed and the sum

along with the timestmp for the threshold crossing are saved.

PL = latency = PL=20 => 200 nsec; time delay to record measurements after trigger is received and time window begins

PTW= 20 => 80 nsecPulse Time width = time interval window for measurements

Assuming the Clock is 250 MHz => clock pulse widths are 4 nsec

faSetProcMode(7,1,40,38,3,6,1,0)

check using the status command

-> faStatus(0) STATUS for FADC in slot 7 at base address 0x90bb0000 -------------------------------------------------- Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 Alternate VME Addressing: Multiblock Disabled A32 Enabled at VME base 0x08000000 or CPU addr 0x80000000 Signal Sources: Ref Clock : Internal Trig Src : VME (Software) Sync Reset: VME (Software) Configuration: Internal Clock ON Bus Error DISABLED MultiBlock transfer DISABLED Software Triggers ENABLED Software Sync Reset ENABLED ADC Processing Configuration: (0x0018 0x0018) Channel Disable Mask = 0x0000 Resolution = 10 bits Mode = 1 (ENABLED) Lookback (PL) = 160 ns Time Window (PTW) = 152 ns Time Before Peak = 12 ns Time After Peak = 24 ns Max Peak Count = 1 CSR Register = 0x006318e0 Control 1 Register = 0x00030eef Control 2 Register = 0x00000000 - Disabled Internal Triggers (Live) = 0 Trigger Scaler = 0 Events in FIFO = 0 (Block level = 1) value = 44 = 0x2c = ','

Trig Src : VME (Software)

Set the internal trigger pulse width

set the internal trigger pulse width to 2 clock ticks (8 ns)

/* * Set Internal trigger pulse width and deadtime between triggers * Range for each : 4ns <-> 1020ns * * Units are in clock ticks (4ns/tick) */ faItrigControl(int id, unsigned short itrig_width, unsigned short itrig_dt)

-> faItrigControl(0, 2, 0 ) value = 131082 = 0x2000a

Enable all channels

-> faEnable(0,0,0)

Generate a software trigger

-> faTrig(0) value = -1866792960 = 0x90bb0000 = tclOpenFiles + 0x82ef31a0

The output was different on 5/6/11:

-> faTrig(0) value = -1866792960 = 0x90bb0000 = fadc_data + 0x82ee9c00

check if there is an event in the FIFO

-> faStatus(0) STATUS for FADC in slot 7 at base address 0x90bb0000 -------------------------------------------------- Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 Alternate VME Addressing: Multiblock Disabled A32 Enabled at VME base 0x08000000 or CPU addr 0x80000000 Signal Sources: Ref Clock : Internal Trig Src : VME (Software) Sync Reset: VME (Software) Configuration: Internal Clock ON Bus Error DISABLED MultiBlock transfer DISABLED Software Triggers ENABLED Software Sync Reset ENABLED ADC Processing Configuration: (0x0018 0x0018) Channel Disable Mask = 0x0000 Resolution = 10 bits Mode = 1 (ENABLED) Lookback (PL) = 160 ns Time Window (PTW) = 152 ns Time Before Peak = 12 ns Time After Peak = 24 ns Max Peak Count = 1 CSR Register = 0x006318e7 Control 1 Register = 0x00030eef Control 2 Register = 0x00000007 - Enabled for triggers Internal Triggers (Live) = 0 Trigger Scaler = 1 Blocks in FIFO = 1 (Block level = 1) - Block Available RAM Level (Bytes) = 0 value = 26 = 0x1a

Now I see an event in the FIFO

Print FIFO status

-> faPrintFifoStatus(0)

Fifo Buffers Status (DataFlow Status = 0x0000013d

Input Buffer : 0x90009000

FPGA1: wc=0 Empty=1 Full=0 Ready=1

FPGA2: wc=0 Empty=1 Full=0 Ready=1

Build Buffer : 0x10001000

FPGA1: wc=0 Empty=1 Full=0

FPGA2: wc=0 Empty=1 Full=0

Output Buffer: 0x20002000

FPGA1: wc=0 Empty=1 Full=0

FPGA2: wc=0 Empty=1 Full=0

value = 34 = 0x22 = '"'

The output on 5/6/11 was:

Fifo Buffers Status (DataFlow Status = 0x0003810d

Input Buffer : 0x90009000

FPGA1: wc=0 Empty=1 Full=0 Ready=1

FPGA2: wc=0 Empty=1 Full=0 Ready=1

Build Buffer : 0x10001000

FPGA1: wc=0 Empty=1 Full=0

FPGA2: wc=0 Empty=1 Full=0

Output Buffer: 0x00900090

FPGA1: wc=144 Empty=0 Full=0

FPGA2: wc=144 Empty=0 Full=0

value = 36 = 0x24 = '$'

Count events ready to be readout

you can count how many events or blocks are ready to be read out with the command

-> faDready(0,0) value = 1 = 0x1

try to read a block

I stil don't see channel 1 or 3 in the output?

-> faPrintBlock(0,0)

81000801 - BLOCK HEADER - slot = 4 n_evts = 1 n_blk = 1

90000008 - EVENT HEADER 1 - evt_num = 8

8 - EVENT HEADER 2 - evt_num = 8

98EEF118 - TRIGGER TIME 1 - time = EEF118

D1E17A - TRIGGER TIME 2 - time = D1E17A

EEF118 - TRIGGER TIME 3 - time = EEF118

D1E17A - TRIGGER TIME 4 - time = D1E17A

A0000026 - WINDOW RAW DATA - chan = 0 nsamples = 38

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

11001100 - RAW SAMPLES - valid = 1 adc = 4352 valid = 1 adc = 4352

A1000026 - WINDOW RAW DATA - chan = 2 nsamples = 38

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

80004 - RAW SAMPLES - valid = 1 adc = 8 valid = 1 adc = 4

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40000 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 0

0 - RAW SAMPLES - valid = 1 adc = 0 valid = 1 adc = 0

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40000 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 0

4 - RAW SAMPLES - valid = 1 adc = 0 valid = 1 adc = 4

4 - RAW SAMPLES - valid = 1 adc = 0 valid = 1 adc = 4

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

80008 - RAW SAMPLES - valid = 1 adc = 8 valid = 1 adc = 8

80004 - RAW SAMPLES - valid = 1 adc = 8 valid = 1 adc = 4

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

A2000026 - WINDOW RAW DATA - chan = 4 nsamples = 38

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

17C017C - RAW SAMPLES - valid = 1 adc = 380 valid = 1 adc = 380

A2800026 - WINDOW RAW DATA - chan = 5 nsamples = 38

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40008 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 8

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40000 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 0

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

80008 - RAW SAMPLES - valid = 1 adc = 8 valid = 1 adc = 8

80008 - RAW SAMPLES - valid = 1 adc = 8 valid = 1 adc = 8

80008 - RAW SAMPLES - valid = 1 adc = 8 valid = 1 adc = 8

80008 - RAW SAMPLES - valid = 1 adc = 8 valid = 1 adc = 8

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40000 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 0

40004 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 4

40008 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 8

40008 - RAW SAMPLES - valid = 1 adc = 4 valid = 1 adc = 8

80008 - RAW SAMPLES - valid = 1 adc = 8 valid = 1 adc = 8

80008 - RAW SAMPLES - valid = 1 adc = 8 valid = 1 adc = 8

80004 - RAW SAMPLES - valid = 1 adc = 8 valid = 1 adc = 4

A3000026 - WINDOW RAW DATA - chan = 6 nsamples = 38

C0010 - RAW SAMPLES - valid = 1 adc = 12 valid = 1 adc = 16

100010 - RAW SAMPLES - valid = 1 adc = 16 valid = 1 adc = 16

10000C - RAW SAMPLES - valid = 1 adc = 16 valid = 1 adc = 12

C0010 - RAW SAMPLES - valid = 1 adc = 12 valid = 1 adc = 16

100010 - RAW SAMPLES - valid = 1 adc = 16 valid = 1 adc = 16

100010 - RAW SAMPLES - valid = 1 adc = 16 valid = 1 adc = 16

100010 - RAW SAMPLES - valid = 1 adc = 16 valid = 1 adc = 16

C000C - RAW SAMPLES - valid = 1 adc = 12 valid = 1 adc = 12

100010 - RAW SAMPLES - valid = 1 adc = 16 valid = 1 adc = 16

100014 - RAW SAMPLES - valid = 1 adc = 16 valid = 1 adc = 20

100010 - RAW SAMPLES - valid = 1 adc = 16 valid = 1 adc = 16

140010 - RAW SAMPLES - valid = 1 adc = 20 valid = 1 adc = 16

100014 - RAW SAMPLES - valid = 1 adc = 16 valid = 1 adc = 20

140010 - RAW SAMPLES - valid = 1 adc = 20 valid = 1 adc = 16

14000C - RAW SAMPLES - valid = 1 adc = 20 valid = 1 adc = 12

140010 - RAW SAMPLES - valid = 1 adc = 20 valid = 1 adc = 16

100014 - RAW SAMPLES - valid = 1 adc = 16 valid = 1 adc = 20

100010 - RAW SAMPLES - valid = 1 adc = 16 valid = 1 adc = 16

C000C - RAW SAMPLES - valid = 1 adc = 12 valid = 1 adc = 12

A3800026 - WINDOW RAW DATA - chan = 7 nsamples = 38

30002C - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 44

30002C - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 44

30002C - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 44

2C0030 - RAW SAMPLES - valid = 1 adc = 44 valid = 1 adc = 48

2C002C - RAW SAMPLES - valid = 1 adc = 44 valid = 1 adc = 44

2C002C - RAW SAMPLES - valid = 1 adc = 44 valid = 1 adc = 44

300030 - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 48

30002C - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 44

300030 - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 48

30002C - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 44

300030 - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 48

300030 - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 48

300030 - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 48

30002C - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 44

300030 - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 48

2C002C - RAW SAMPLES - valid = 1 adc = 44 valid = 1 adc = 44

2C002C - RAW SAMPLES - valid = 1 adc = 44 valid = 1 adc = 44

300030 - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 48

300030 - RAW SAMPLES - valid = 1 adc = 48 valid = 1 adc = 48

A4000026 - WINDOW RAW DATA - chan = 8 nsamples = 38

CC00CC - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 204

CC00CC - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 204

CC00CC - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 204

CC00CC - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 204

CC00CC - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 204

C800D0 - RAW SAMPLES - valid = 1 adc = 200 valid = 1 adc = 208

CC00CC - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 204

CC00CC - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 204

CC00C8 - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 200

CC00CC - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 204

CC00CC - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 204

CC00CC - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 204

CC00CC - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 204

CC00C8 - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 200

CC00D0 - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 208

CC00CC - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 204

CC00CC - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 204

CC00D0 - RAW SAMPLES - valid = 1 adc = 204 valid = 1 adc = 208

D000D0 - RAW SAMPLES - valid = 1 adc = 208 valid = 1 adc = 208

A5000026 - WINDOW RAW DATA - chan = 10 nsamples = 38

E400E0 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 224

E400E4 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 228

E400E8 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 232

E400E4 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 228

E400E4 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 228

E400E4 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 228

E800E4 - RAW SAMPLES - valid = 1 adc = 232 valid = 1 adc = 228

E400E4 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 228

E400E4 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 228

E400E4 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 228

E400E4 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 228

E400E8 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 232

E800E8 - RAW SAMPLES - valid = 1 adc = 232 valid = 1 adc = 232

E400E4 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 228

E000E0 - RAW SAMPLES - valid = 1 adc = 224 valid = 1 adc = 224

E400E4 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 228

E400E4 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 228

E400E4 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 228

E400E8 - RAW SAMPLES - valid = 1 adc = 228 valid = 1 adc = 232

A5800026 - WINDOW RAW DATA - chan = 11 nsamples = 38

C400C8 - RAW SAMPLES - valid = 1 adc = 196 valid = 1 adc = 200

C400C4 - RAW SAMPLES - valid = 1 adc = 196 valid = 1 adc = 196

C800C4 - RAW SAMPLES - valid = 1 adc = 200 valid = 1 adc = 196

C400C8 - RAW SAMPLES - valid = 1 adc = 196 valid = 1 adc = 200

C800C4 - RAW SAMPLES - valid = 1 adc = 200 valid = 1 adc = 196

C800C8 - RAW SAMPLES - valid = 1 adc = 200 valid = 1 adc = 200

C800C8 - RAW SAMPLES - valid = 1 adc = 200 valid = 1 adc = 200

C800C8 - RAW SAMPLES - valid = 1 adc = 200 valid = 1 adc = 200

C800C8 - RAW SAMPLES - valid = 1 adc = 200 valid = 1 adc = 200

C400C8 - RAW SAMPLES - valid = 1 adc = 196 valid = 1 adc = 200

C800C8 - RAW SAMPLES - valid = 1 adc = 200 valid = 1 adc = 200

C800C8 - RAW SAMPLES - valid = 1 adc = 200 valid = 1 adc = 200

C800C8 - RAW SAMPLES - valid = 1 adc = 200 valid = 1 adc = 200

C800C8 - RAW SAMPLES - valid = 1 adc = 200 valid = 1 adc = 200

C400C8 - RAW SAMPLES - valid = 1 adc = 196 valid = 1 adc = 200

C800C8 - RAW SAMPLES - valid = 1 adc = 200 valid = 1 adc = 200

C400C4 - RAW SAMPLES - valid = 1 adc = 196 valid = 1 adc = 196

C400C8 - RAW SAMPLES - valid = 1 adc = 196 valid = 1 adc = 200

C400C8 - RAW SAMPLES - valid = 1 adc = 196 valid = 1 adc = 200

A6000026 - WINDOW RAW DATA - chan = 12 nsamples = 38

B000AC - RAW SAMPLES - valid = 1 adc = 176 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

A800AC - RAW SAMPLES - valid = 1 adc = 168 valid = 1 adc = 172

AC00A8 - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 168

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00B0 - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 176

B000AC - RAW SAMPLES - valid = 1 adc = 176 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00A8 - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 168

A800AC - RAW SAMPLES - valid = 1 adc = 168 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00A8 - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 168

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

A800AC - RAW SAMPLES - valid = 1 adc = 168 valid = 1 adc = 172

A6800026 - WINDOW RAW DATA - chan = 13 nsamples = 38

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00B0 - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 176

B000AC - RAW SAMPLES - valid = 1 adc = 176 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00B0 - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 176

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00B0 - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 176

AC00B0 - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 176

B000B0 - RAW SAMPLES - valid = 1 adc = 176 valid = 1 adc = 176

B000B0 - RAW SAMPLES - valid = 1 adc = 176 valid = 1 adc = 176

B000AC - RAW SAMPLES - valid = 1 adc = 176 valid = 1 adc = 172

B000B0 - RAW SAMPLES - valid = 1 adc = 176 valid = 1 adc = 176

AC00AC - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 172

AC00A8 - RAW SAMPLES - valid = 1 adc = 172 valid = 1 adc = 168

A7000026 - WINDOW RAW DATA - chan = 14 nsamples = 38

B400B4 - RAW SAMPLES - valid = 1 adc = 180 valid = 1 adc = 180

B400B4 - RAW SAMPLES - valid = 1 adc = 180 valid = 1 adc = 180

B800B8 - RAW SAMPLES - valid = 1 adc = 184 valid = 1 adc = 184

B400B4 - RAW SAMPLES - valid = 1 adc = 180 valid = 1 adc = 180

B400B4 - RAW SAMPLES - valid = 1 adc = 180 valid = 1 adc = 180

B800B4 - RAW SAMPLES - valid = 1 adc = 184 valid = 1 adc = 180

B400B8 - RAW SAMPLES - valid = 1 adc = 180 valid = 1 adc = 184

B400B8 - RAW SAMPLES - valid = 1 adc = 180 valid = 1 adc = 184

B800B4 - RAW SAMPLES - valid = 1 adc = 184 valid = 1 adc = 180

B400B8 - RAW SAMPLES - valid = 1 adc = 180 valid = 1 adc = 184

B400B8 - RAW SAMPLES - valid = 1 adc = 180 valid = 1 adc = 184

B800BC - RAW SAMPLES - valid = 1 adc = 184 valid = 1 adc = 188

B400B8 - RAW SAMPLES - valid = 1 adc = 180 valid = 1 adc = 184

B400B8 - RAW SAMPLES - valid = 1 adc = 180 valid = 1 adc = 184

B400B4 - RAW SAMPLES - valid = 1 adc = 180 valid = 1 adc = 180

B400B4 - RAW SAMPLES - valid = 1 adc = 180 valid = 1 adc = 180

B800B4 - RAW SAMPLES - valid = 1 adc = 184 valid = 1 adc = 180

B800B4 - RAW SAMPLES - valid = 1 adc = 184 valid = 1 adc = 180

B400B8 - RAW SAMPLES - valid = 1 adc = 180 valid = 1 adc = 184

A7800026 - WINDOW RAW DATA - chan = 15 nsamples = 38

A0009C - RAW SAMPLES - valid = 1 adc = 160 valid = 1 adc = 156

A000A0 - RAW SAMPLES - valid = 1 adc = 160 valid = 1 adc = 160

A000A0 - RAW SAMPLES - valid = 1 adc = 160 valid = 1 adc = 160

A000A0 - RAW SAMPLES - valid = 1 adc = 160 valid = 1 adc = 160

A000A0 - RAW SAMPLES - valid = 1 adc = 160 valid = 1 adc = 160

A000A0 - RAW SAMPLES - valid = 1 adc = 160 valid = 1 adc = 160

A000A0 - RAW SAMPLES - valid = 1 adc = 160 valid = 1 adc = 160

A0009C - RAW SAMPLES - valid = 1 adc = 160 valid = 1 adc = 156

A000A0 - RAW SAMPLES - valid = 1 adc = 160 valid = 1 adc = 160

9C009C - RAW SAMPLES - valid = 1 adc = 156 valid = 1 adc = 156

9C00A0 - RAW SAMPLES - valid = 1 adc = 156 valid = 1 adc = 160

A000A0 - RAW SAMPLES - valid = 1 adc = 160 valid = 1 adc = 160

9C009C - RAW SAMPLES - valid = 1 adc = 156 valid = 1 adc = 156

A000A0 - RAW SAMPLES - valid = 1 adc = 160 valid = 1 adc = 160

A000A0 - RAW SAMPLES - valid = 1 adc = 160 valid = 1 adc = 160

A400A0 - RAW SAMPLES - valid = 1 adc = 164 valid = 1 adc = 160

A400A0 - RAW SAMPLES - valid = 1 adc = 164 valid = 1 adc = 160

A400A4 - RAW SAMPLES - valid = 1 adc = 164 valid = 1 adc = 164

A000A4 - RAW SAMPLES - valid = 1 adc = 160 valid = 1 adc = 164

89000120 - BLOCK TRAILER - slot = 4 n_words = 288

value = 288 = 0x120

Hardware Trigger

Install DMA lib

Configure ROC

Load the library

-> ld < usrTempeDma.o value = 230900496 = 0xdc34310

Configure the Memory

-> usrVmeDmaConfig(2,2,0) 0xdbb1830 (tShell): VME DMA Address Mode set for A32 0xdbb1830 (tShell): VME DMA Transfer Mode set for D32 block mode (BLT) value = 0 = 0x0

Show the Dma config

-> sysVmeDmaShow DMA Chan 0 Status = 0x00290000 Source(VME) address: 0x002b0000 Destination address: 0x0020efb4 Byte Count : 0x00007356 Execption Status : 0x00000000 Bus Error address: 0x00000000 DMA Control Reg : 0x00000000 VME Address Mode : 2 (A32) VME Data Width : 1 (D32) VME Transfer Mode: 1 (BLT32) STATUS of Last Transfer: NO Transfer Completed value = 2686976 = 0x290000 -> ld < fadcLib.o value = 230935520 = 0xdc3cbe0

- Click Prestart

daLogMsg: INFO: Entering User Prestart linking async GEN trigger to id 1 disconnecting vector 225 STATUS for FADC in slot 7 at base address 0x90bb0000 -------------------------------------------------- Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 Alternate VME Addressing: Multiblock Disabled A32 Enabled at VME base 0x08000000 or CPU addr 0x80000000 Signal Sources: Ref Clock : Front Panel Trig Src : Front Panel (Async) Sync Reset: Front Panel (Async) SDC : In Use Configuration: Internal Clock ON Bus Error ENABLED MultiBlock transfer DISABLED ADC Processing Configuration: (0x0018 0x0018) Channel Disable Mask = 0x0000 Resolution = 10 bits Mode = 1 (ENABLED) Lookback (PL) = 200 ns Time Window (PTW) = 80 ns Time Before Peak = 12 ns Time After Peak = 24 ns Max Peak Count = 1 CSR Register = 0x006318e0 Control 1 Register = 0x00130119 Control 2 Register = 0x0000000f - Enabled for triggers Internal Triggers (Live) = 0 Trigger Scaler = 0 Events in FIFO = 0 (Block level = 1)

- Click Go

daLogMsg: INFO: Entering User Go 0xdca6890 (ROC): faSync: ERROR: Software Sync Resets not enabledinterrupt: ERROR: NO data in FADC datascan = 0x0

now trigger one time

-> faStatus(0)

STATUS for FADC in slot 7 at base address 0x90bb0000

--------------------------------------------------

Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909

Alternate VME Addressing: Multiblock Disabled

A32 Enabled at VME base 0x08000000 or CPU addr 0x80000000

Signal Sources:

Ref Clock : Front Panel

Trig Src : Front Panel (Async)

Sync Reset: Front Panel (Async)

SDC : In Use

Configuration:

Internal Clock ON

Bus Error ENABLED

MultiBlock transfer DISABLED

ADC Processing Configuration: (0x0018 0x0018)

Channel Disable Mask = 0x0000

Resolution = 10 bits

Mode = 1 (ENABLED)

Lookback (PL) = 200 ns Time Window (PTW) = 80 ns

Time Before Peak = 12 ns Time After Peak = 24 ns

Max Peak Count = 1

CSR Register = 0x006318e8

Control 1 Register = 0x00130119

Control 2 Register = 0x0000000f - Enabled for triggers

Internal Triggers (Live) = 0

Trigger Scaler = 1

Events in FIFO = 0 (Block level = 1)

value = 44 = 0x2c = ','

-> sysVmeDmaShow

DMA Chan 0 Status = 0x10000000

Source(VME) address: 0x08000800

Destination address: 0x0d152e30

Byte Count : 0x00003680

Execption Status : 0x000ccb00

Bus Error address: 0x080002b8

DMA Control Reg : 0x00836070

VME Address Mode : 2 (A32)

VME Data Width : 1 (D32)

VME Transfer Mode: 1 (BLT32)

STATUS of Last Transfer:

Error Bit Set

Source: VME Bus

value = 268435456 = 0x10000000

There is an error bit set.

- Second Trigger

no change

- Third Trigger

-> interrupt: ERROR: Data still in FADC (event 4, scan 0x1 csr 0xf06318ef ) - clearing

ROC crashes

Setup Signal distribution board

FADC and SD address

The ADC address pins are set to

| Address | ||

| Pin | Switch | bit |

| A12 | on/closed | 0 |

| A13 | on | 0 |

| A14 | on | 0 |

| A15 | on | 0 |

| A16 | off | 1 |

| A17 | off/open | 1 |

| A18 | on | 0 |

| A19 | off | 1 |

| A20 | off | 1 |

| A21 | off | 1 |

| A22 | on | 0 |

| A23 | off | 1 |

0xbb000 =101110110000000000000000

The signal distribution board SDC is set to

| Address | ||

| Pin | Switch | bit |

| A6 | on/closed | 0 |

| A7 | on | 0 |

| A8 | on | 0 |

| A9 | off | 1 |

| A10 | on | 0 |

| A11 | off/open | 1 |

| A12 | on | 0 |

| A13 | off | 1 |

| A14 | off | 1 |

| A15 | off | 1 |

0xea = 1110101000

Initialize FADC for Front panel(FP) trigger with Signal distribution (SD) board

The address of the SD board is passed to the faInit routine

Using the SD boards's internal clock

-> faInit(0xbb0000,0,0,0xea13) Initialized FADC 0 Slot # 7 at address 0x90bb0000 Using JLAB FADC Signal Distribution Module at address 0x9100ea00 faInit: JLAB FADC Signal Distribution Card is Assumed in Use faInit: Front Panel Inputs will be enabled. faInit: Enabling FADC for SDC Clock (Front Panel) and Front Panel Triggers (FP Sync Reset) value = 0 = 0x0

or using the FADC's internal clock

-> faInit(0xbb0000,0,0,0xea03) Initialized FADC 0 Slot # 7 at address 0x90bb0000 Using JLAB FADC Signal Distribution Module at address 0x9100ea00 faInit: JLAB FADC Signal Distribution Card will not be Used faInit: Enabling FADC Internal Clock, and Front Panel Triggers (FP Sync Reset) value = 0 = 0x0

faSDC_Status

-> faSDC_Status(0) STATUS for FADC Signal Distribution Card at base address 0x9100ea00 ---------------------------------------------------------------- Board Firmware Rev/ID = 0x02 Registers: CSR = 0x0200 Control = 0x0220 Busy Enable = 0x0000 Busy Status = 0xfe00 Ref Clock : Internal Software Triggers Software Sync Reset value = 21 = 0x15

The SDC has not been eneabled yet for external triggers.

Use faGEnable(0,0) to enable both the FADC and the SD board

-> faGEnable(0,0) value = 1 = 0x1

-> faSDC_Status(0)

STATUS for FADC Signal Distribution Card at base address 0x9100ea00

Board Firmware Rev/ID = 0x02 Registers: CSR = 0x0200 Control = 0x0200 Busy Enable = 0x0000 Busy Status = 0xfe00

Ref Clock : Internal External Triggers (Sync with clock) Software Sync Reset

value = 21 = 0x15

Set the FADC processing mode

-> faSetProcMode(7,1,40,38,3,6,1,0) value = 0 = 0x0

int

faSetProcMode(int id, int pmode, unsigned int PL, unsigned int PTW,

unsigned int NSB, unsigned int NSA, unsigned int NP, int bank)

id = slot number =7

An example of this should be in one of the Readout lists, however, right now there are 3 viable processing modes (pmode =1,2 or 3)

pmode = 1 RAW Window mode: all samples within PTW are saved

pmode = 2 RAW Pulse mode: NSA+NSB+1 samples around a threshold crossing

are saved.

pmode = 3 Integral pulse mode: NSA+NSB+1 samples are summed and the sum

along with the timestmp for the threshold crossing are saved.

PL = 40 = 160 ns = programmable latency ; time delay to record measurements after trigger is received and time window begins

PTW= 20 => 80 nsecPulse Time width = time interval window for measurements

= number of samples in the pulse time window moving forward in time from the location of the latency.

NSB = 3 = Number of Samples before before the pulse to record

NSA=6 = number of samples after the pulse to record

NP =1 = number of pulses to look for in the PTW

Assuming the Clock is 250 MHz => clock pulse widths are 4 nsec

Configure SD card

/***************************************************************************************

JLAB FADC Signal Distribution Card (SDC) Routines

cFlag: controls the configuation of the SDC

0: Default Mode Internal CLK, Sync External Trigger and Sync Reset

> 0: Pass through mode

bMask: mask of Busy enables for the SDC - Do not Enable busy if there is no FADC

*/

int

faSDC_Config(unsigned short cFlag, unsigned short bMask)

-> faSDC_Config(0,0)

value = 0 = 0x0

FADC status

-> faStatus(0) STATUS for FADC in slot 7 at base address 0x90bb0000 -------------------------------------------------- Board Firmware Rev/ID = 0x0114 : ADC Processing Rev = 0x0909 Alternate VME Addressing: Multiblock Disabled A32 Enabled at VME base 0x08000000 or CPU addr 0x80000000 Signal Sources: Ref Clock : Front Panel Trig Src : Front Panel (Async) Sync Reset: Front Panel (Async) SDC : In Use Configuration: Internal Clock ON Bus Error DISABLED MultiBlock transfer DISABLED ADC Processing Configuration: (0x0018 0x0018) Channel Disable Mask = 0x0000 Resolution = 10 bits Mode = 1 (ENABLED) Lookback (PL) = 160 ns Time Window (PTW) = 152 ns Time Before Peak = 12 ns Time After Peak = 24 ns Max Peak Count = 1 CSR Register = 0x00631ce0 Control 1 Register = 0x00030119 Control 2 Register = 0x00000007 - Enabled for triggers Internal Triggers (Live) = 0 Trigger Scaler = 0 Events in FIFO = 0 (Block level = 1) value = 44 = 0x2c = ','

Test pulse Measurment

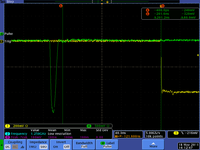

Input the test pulse below into the FADC

I set a delay for 200 ns and a pulse window for 40 ns.

faSetProcMode(7,1,50,10,0,0,0,0); ADC Processing Configuration: (0xfe08 0xff08) Channel Disable Mask = 0xfffe Resolution = 10 bits Mode = 1 (ENABLED) Lookback (PL) = 200 ns Time Window (PTW) = 40 ns Time Before Peak = 20 ns Time After Peak = 40 ns Max Peak Count = 0

RUn 2144 with 64 events

Run 2145 with

faChanDisable

One can disable ADC channels using the function

faChanDisable(ID,mask)

where mask is a word representing which channels you should disable with the high bit.

all 16 channels are disables with 0xffff

only channel 0 is enabled with

faChanDidable(0,0xfffe)

Documentation

Data Format

header bank ID is =38797568=0x2500100

File:JLab F250 ADC V1.2 DataFormat.pdf

Decoding an Event

0x00000000 0xf800fafa 0x81c00801 0x90000007 0x00000007 0x980000be 0x0001f922 0x000000be 0x0001f922 0xa0000014 0x11001100 0x11001100 0x11001100 0x11001100 0x11001100 0x11001100 0x11001100 0x11001100 0x11001100 0x11001100 0xa1000014 0x00080008 0x00040008 0x000c0008 0x00080008 0x00040008 0x00080008 0x00040004 0x00040004 0x00080004 0x00040004 0xa1800014 0x10000004 0x10000000 0x10001000 0x10001000 0x10001000 0x10001000 0x10000000 0x00000000 0x10001000 0x00001000 0xa2000014 0x00cc00cc 0x00cc00d0 0x00cc00cc 0x00cc00cc 0x00cc00d0 0x00cc00cc 0x00cc00cc 0x00cc00cc 0x00cc00d0 0x00cc00cc 0xa2800014 0x00080008 0x00040008 0x00040004 0x00080004 0x00080008 0x00080008 0x00040004 0x00040008 0x00040008 0x00040008 0xa3000014 0x00140014 0x00140010 0x00140014 0x00140010 0x00100014 0x00140014 0x00140014 0x00140014 0x00140014 0x00180018 0xa3800014 0x0028002c 0x0028002c 0x002c0028 0x002c002c 0 x002c002c 0x002c002c 0x002c002c 0x002c002c 0x0028002c 0x002c002c 0xa4000014 0x00cc00cc 0x00cc00c8 0x00cc00cc 0x00c800cc 0x00cc00cc 0x00d000cc 0x00cc00c8 0x00cc00cc 0x00cc00cc 0x00cc00cc 0xa4800014 0x00cc00cc 0x00cc00cc 0x00c800c8 0x00cc00cc 0x00cc00cc 0x00cc00cc 0x00cc00cc 0x00cc00cc 0x00c800cc 0x00cc00c8 0xa5000014 0x00e400e4 0x00e400e4 0x00e400e4 0x00e400e8 0x00e400e4 0x00e800e4 0x00e400e4 0x00e000e4 0x00e400e4 0x00e400e4 0xa5800014 0x00c800cc 0x00c800cc 0x00cc00c8 0x00c800cc 0x00cc00c8 0x00c800cc 0x00c800cc 0x00c800cc 0x00c800c8 0x00cc00cc 0xa6000014 0x00b000b0 0x00ac00b0 0x00b000b0 0x00ac00ac 0x00b000b0 0x00ac00ac 0x00ac00ac 0x00b000b0 0x00b000ac 0x00b000b0 0xa6800014 0x00ac00b0 0x00b000ac 0x00ac00ac 0x00b000b0 0x00b000b0 0x00b000ac 0x00ac00ac 0x00b000ac 0x00b000b0 0x00ac00ac 0xa7000014 0x00b800b8 0x00b400b4 0x00b400bc 0x00bc00bc 0x00b800b8 0x00b400b8 0x00b800b8 0x00b800b8 0x00b800b8 0x00b800b8 0xa7800014 0x00a000a0 0x00a400a0 0x00a000a0 0x00a000a4 0x00a400a4 0x00a400a4 0x00a000a0 0x00a000a0 0x00a000a0 0x00a400a0 0xf800ffff 0x89c000ae

Readoutlist example

___________________________________________________________________

| |

| Jefferson Lab Tel: (757) 269-7159 |

| Riad Suleiman FAX: (757) 269-5520 |

| 12050 Jefferson Ave |

| Suite 500 |

| Newport News, VA 23606 Email:suleiman@jlab.org |

| Text Pager: 7572893892@messaging.nextel.com |

| http://www.jlab.org/~suleiman |

| Home: (757) 865-0355 |

-------------------------------------------------------------------

# Source for generic VME readout using a

# TJNAF trigger supervisor interface register (TIR)

# as a source for external interrupts

#

# David Abbott, TJNAF 1996

readout list VME1

maximum 16384,400

vme readout

#polling

#ts control

const TIR_ADDR = 0x0ed0

const FADC_ADDR = 0xee0000

const FADC_BLOCK_MODE = 1

const MAX_FADC_DATA = 4000

extern int bigendian_out;

extern int fadcID[20];

int FA_SLOT;

begin download

variable res

# If the ROC is sending data to Little-Endian EB

# e.g. a x86 Linux CPU then bigendian_out = 0.

# Unless the ROC is also running on a Little-Endian

# machine. Then set bigendian_out=1.

bigendian_out = 0;

# Setup TIR

tirInit(TIR_ADDR);

# Initialize FADC library and Modules for standalone

# and Front Panel Triggers

faInit(FADC_ADDR,0,1,0xea13);

FA_SLOT = fadcID[0];

log inform "User Download Executed"

end download

begin prestart

log inform "Entering User Prestart"

init trig source VME

link async trig source VME 1 to usrtrig and usrtrig_done

event type 1 then read VME 1

# Assume FADCs have been Initialized at boot or in download

# Setup FADC Programming

faSetBlockLevel(FA_SLOT,1);

# for Block Reads

faEnableBusError(FA_SLOT);

# for Single Cycle Reads

# faDisableBusError(FA_SLOT);

# Set All channel thresholds to 0

faSetThreshold(FA_SLOT,0,0xffff);

# Setup option 1 processing - RAW Window Data <--

# option 2 - RAW Pulse Data

# option 3 - Integral Pulse Data

# Setup 120 nsec latency (PL = 30)

# Setup 80 nsec Window (PTW = 20)

# Setup Pulse widths of 36ns (NSB(3)+NSA(6) = 9)

# Setup up to 1 pulse processed

# Setup for both ADC banks(0 - all channels 0-15)

faSetProcMode(FA_SLOT,1,40,38,3,6,1,0);

# Print out status

faStatus(FA_SLOT,0);

log inform "User Prestart Executed"

end prestart

begin end

CDODISABLE(VME,1,0);

#FADC Disable

faGDisable(0,0);

#FADC Event status - Is all data read out

faStatus(FA_SLOT,0);

log inform "User End Executed"

end end

begin pause

CDODISABLE(VME,1,0);

log inform "User Pause Executed"

end pause

begin go

variable outval

log inform "Entering User Go"

# Enable FADCs

faGEnable(0,0);

taskDelay(1);

# Send Sync Reset to FADC

faSDC_Sync();

taskDelay(1);

CDOENABLE(VME,1,0);

end go

begin trigger usrtrig

variable ii, stat, csr

rol->dabufp = (long *) 0;

open event type EVTYPE of BT_UI4

%%

int nwrds=0;

/* Check if a Block of data is available */

for(ii=0;ii<100;ii++) {

stat = faBready(FA_SLOT);

if (stat>0) {

*rol->dabufp++ = ii;

break;

}

}

if(stat > 0) {

nwrds = faReadBlock(FA_SLOT,rol->dabufp,MAX_FADC_DATA,FADC_BLOCK_MODE);

if(nwrds<=0) {

logMsg("ERROR: FADC Block Read Failed - Status 0x%x\n",nwrds,0,0,0,0,0);

*rol->dabufp++ = 0xda000bad;

faClear(FA_SLOT);