Difference between revisions of "JLAB PLX LVDS"

Jump to navigation

Jump to search

| Line 8: | Line 8: | ||

[[Media:PLX_BoardLayout.pdf]] | [[Media:PLX_BoardLayout.pdf]] | ||

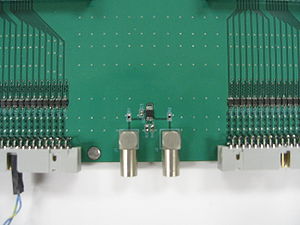

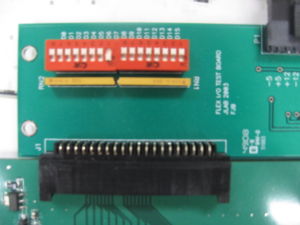

| + | [[Image:PLX1.jpg|300px]][[Image:PLX_2.jpg|300px]] | ||

| + | |||

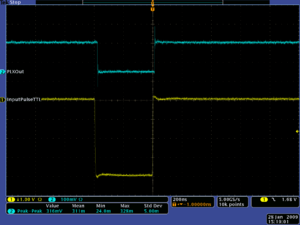

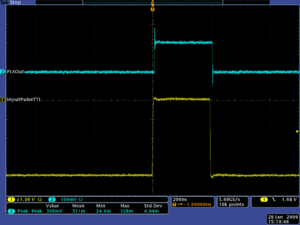

| + | [[Image:PLX_3.jpg|300px]][[Image:PLX_4.jpg|300px]] | ||

| + | |||

| + | [[Image:PLX_5.jpg|300px]] | ||

| + | |||

| + | [[Image:PLX_input_and_output_pulses.png|300px]] | ||

| + | |||

| + | |||

| + | [[Image:PLX_input_and_output_pulses_1.png|300px]] | ||

[http://wiki.iac.isu.edu/index.php/VME_modules Go back] | [http://wiki.iac.isu.edu/index.php/VME_modules Go back] | ||

[[VME_modules]] Go back | [[VME_modules]] Go back | ||

Revision as of 03:54, 29 January 2009

A VME Modules designed by Ed Jastrzembski at JLAB

Description:

This PLX board will be built on a Flex I/O format that Ed Jastrzembski developed many years ago. The VME (back end) manages the interface to the bus, and controls two front end 'ports' that can be input or output units.

Go back VME_modules Go back