Difference between revisions of "CAEN V775 TDC"

Jump to navigation

Jump to search

| Line 45: | Line 45: | ||

Last Event Read = (No Events Read) | Last Event Read = (No Events Read) | ||

value = 37 = 0x25 = '%' | value = 37 = 0x25 = '%' | ||

| + | |||

| + | = Read Data = | ||

| + | |||

Revision as of 01:38, 25 November 2008

| Address | |

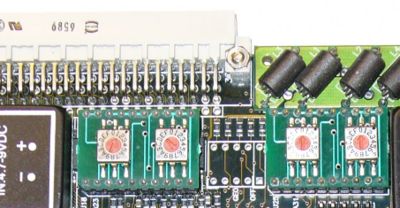

| Pin | Setting |

| SW 1 | 1 |

| SW 2 | 6 |

| SW 3 | 0 |

| SW 4 | 8 |

initialize TDC

-> c775Init(0x610000) Initialized TDC ID 0 at address 0x90610000

Common Start/Stop =

BitSet 2 is used to set the TDC in common start or stop mode.

0 => common start

1 => common start

Use the Status function to see what the bit is set at

-> c775Status(0)

STATUS for TDC id 0 at base address 0x90610000

----------------------------------------------

Interrupts Disabled

Last Interrupt Count : 0

--1-- --2--

Status = 0x0050 0x0002

BitSet = 0x0000 0x0898

Control = 0x0000

FSR = 140 nsec

Event Count = (No Events Taken)

Last Event Read = (No Events Read)

value = 37 = 0x25 = '%'

Read Data

BitSet 2 is set to 0x0898 = 100010011000 d

The above has bit 10 ( starting from 0 at the very left) set to 0 => common start