Difference between revisions of "CAEN V785N ADC"

Jump to navigation

Jump to search

| (2 intermediate revisions by the same user not shown) | |||

| Line 25: | Line 25: | ||

==Data Format== | ==Data Format== | ||

| + | |||

| + | old run on daq1 | ||

| + | |||

| + | /data/olddata/r6xxx/r6998.dat | ||

| + | |||

| + | <pre> | ||

| + | Found CAEN 785 bank with length 19 | ||

| + | Header says 0xfa001000 => 16 converted channels | ||

| + | ADC Ch:0 valid=0 value=83 f8004053 | ||

| + | ADC Ch:8 valid=0 value=74 f810404a | ||

| + | ADC Ch:1 valid=0 value=72 f8024048 | ||

| + | ADC Ch:9 valid=0 value=78 f812404e | ||

| + | ADC Ch:2 valid=0 value=79 f804404f | ||

| + | ADC Ch:10 valid=0 value=68 f8144044 | ||

| + | ADC Ch:3 valid=0 value=283 f806411b | ||

| + | ADC Ch:11 valid=0 value=75 f816404b | ||

| + | ADC Ch:4 valid=0 value=63 f808403f | ||

| + | ADC Ch:12 valid=0 value=65 f8184041 | ||

| + | ADC Ch:5 valid=0 value=71 f80a4047 | ||

| + | ADC Ch:13 valid=0 value=58 f81a403a | ||

| + | ADC Ch:6 valid=0 value=64 f80c4040 | ||

| + | ADC Ch:14 valid=0 value=81 f81c4051 | ||

| + | ADC Ch:7 valid=0 value=84 f80e4054 | ||

| + | </pre> | ||

| + | {| border="1" |cellpadding="20" cellspacing="0 | ||

| + | |colspan= "2" | Address | ||

| + | |- | ||

| + | | Module|| address | ||

| + | |- | ||

| + | |V775 || 0x610000 | ||

| + | |- | ||

| + | |V785 || 0x20000 | ||

| + | |- | ||

| + | |V792 || 0xee0000 | ||

| + | |- | ||

| + | |V260 || 0xda0000 | ||

| + | |- | ||

| + | |V1495 || 0x80110000 | ||

| + | |- | ||

| + | |VX1190 || 0x210000 | ||

| + | |- | ||

| + | |SIS3610 || 0x3800 | ||

| + | |- | ||

| + | |JlabF250 || 0 | ||

| + | |- | ||

| + | |Struck3332|| 0x40 | ||

| + | |} | ||

| Line 57: | Line 104: | ||

const PDC_ADDR = 0x0200000 | const PDC_ADDR = 0x0200000 | ||

| + | |||

| + | SW2 (Bits 19-16) =0 | ||

| + | |||

| + | SW3 (bits 23-20) =2 | ||

| + | |||

| + | SW4 (bits 27-24) =0 | ||

| + | |||

| + | SW5 (bits 31-28) =0 | ||

| + | |||

=Library functions= | =Library functions= | ||

Latest revision as of 22:41, 11 May 2021

CAEN peak sensing multi event ADC

Documentation & Specs

http://www.caentechnologies.com/csite/CaenProd.jsp?parent=11&idmod=285

Specs:

0-> +4 Volt input

5.7 us conversion time

12 Bit ADC

50 nsec min rise time for input pulse

1 k-Ohm input impedance

250 nsec min gate width

1 msec Max gate width

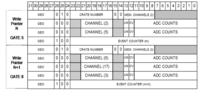

Data Format

old run on daq1

/data/olddata/r6xxx/r6998.dat

Found CAEN 785 bank with length 19 Header says 0xfa001000 => 16 converted channels ADC Ch:0 valid=0 value=83 f8004053 ADC Ch:8 valid=0 value=74 f810404a ADC Ch:1 valid=0 value=72 f8024048 ADC Ch:9 valid=0 value=78 f812404e ADC Ch:2 valid=0 value=79 f804404f ADC Ch:10 valid=0 value=68 f8144044 ADC Ch:3 valid=0 value=283 f806411b ADC Ch:11 valid=0 value=75 f816404b ADC Ch:4 valid=0 value=63 f808403f ADC Ch:12 valid=0 value=65 f8184041 ADC Ch:5 valid=0 value=71 f80a4047 ADC Ch:13 valid=0 value=58 f81a403a ADC Ch:6 valid=0 value=64 f80c4040 ADC Ch:14 valid=0 value=81 f81c4051 ADC Ch:7 valid=0 value=84 f80e4054

| Address | |

| Module | address |

| V775 | 0x610000 |

| V785 | 0x20000 |

| V792 | 0xee0000 |

| V260 | 0xda0000 |

| V1495 | 0x80110000 |

| VX1190 | 0x210000 |

| SIS3610 | 0x3800 |

| JlabF250 | 0 |

| Struck3332 | 0x40 |

| Address | |

| Module | address |

| V775 | 0x610000 |

| V785 | 0x20000 |

| V792 | 0xee0000 |

| V260 | 0xda0000 |

| V1495 | 0x80110000 |

| VX1190 | 0x210000 |

| SIS3610 | 0x3800 |

| JlabF250 | 0 |

| Struck3332 | 0x40 |

Address

const PDC_ADDR = 0x0200000

SW2 (Bits 19-16) =0

SW3 (bits 23-20) =2

SW4 (bits 27-24) =0

SW5 (bits 31-28) =0

Library functions

c785Clear(ADC_ID);

c785ClearThresh(ADC_ID); /* Zero c785 thresholds for all channels*/

c785Enable(ADC_ID);

c785Status(ADC_ID,0,0);

stat = c785Dready(ADC_ID);

if(stat > 0) {

nwrds = c785ReadEvent(ADC_ID,rol->dabufp);

if(nwrds<=0) {

logMsg("ERROR: ADC Read Failed - Status 0x%x\n",nwrds,0,0,0,0,0);

c785Clear(ADC_ID);

} else {

rol->dabufp += nwrds;

}

}else{

logMsg("ERROR: NO data in ADC datascan = 0x%x\n",stat,0,0,0,0,0);

c785Clear(ADC_ID)

}

Standalone functions on 2.6.2

A standalone program was created to test the peak sensing ADC functions in the library on the CODA 2.6.2 ROC

error message:

initializing the SIS3610 Initialized SIS3610 ID 0 at VME (USER) address 0x3800 (0xacfbb800) gefVmeAttachCallback failed: code 0x3010000b ERROR: vmeIntConnect failed